# InP–InGaAs Single HBT Technology for Photoreceiver OEIC's at 40 Gb/s and Beyond

D. Huber, R. Bauknecht, C. Bergamaschi, M. Bitter, A. Huber, T. Morf, A. Neiger, M. Rohner, I. Schnyder, V. Schwarz, and H. Jäckel

**Abstract**—We describe an advanced InP–InGaAs-based technology for the monolithic integration of pin-photodiodes and SHBT-transistors. Both devices are processed using the same epitaxial grown layer structure. Employing this technology, we have designed and fabricated two photoreceivers achieving transimpedance gains of  $170 \Omega/380 \Omega$  and optical/electrical bandwidths of 50 GHz/34 GHz. To the best of our knowledge, this is the highest bandwidth of any heterojunction bipolar transistor (HBT)-based photoreceiver optoelectronic integrated circuit (OEIC) published to date. We even predict a bandwidth of 60 GHz for the same circuit topology by a simple reduction of the photodiode diameter and an adjustment of the feedback resistor value.

**Index Terms**—Heterojunction bipolar transistor (HBT), InP, optoelectronic integrated circuit (OEIC), photoreceiver, processing, transimpedance amplifier.

## I. INTRODUCTION

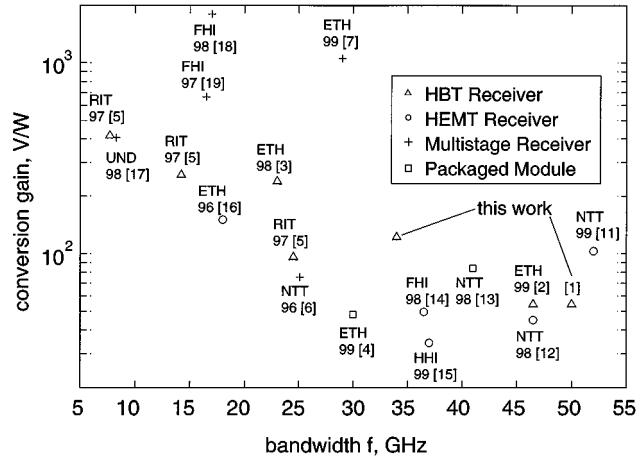

**P**HOTORECEIVER circuits are key-components in fiber optic transmission systems. The exponentially growing demand for higher data rates makes bandwidth to the most important figure of merit for such optoelectronic integrated circuit (OEIC), whereas sensitivity and gain have become a slightly lower priority due to the introduction of erbium-doped fiber amplifiers (EDFA's). Being the first amplification stage in a chain, the noise figure of the optical amplifier dominates the overall sensitivity of the system. In addition, optical gains of 20 dB and more achieved by EDFA's relax the gain requirements for following electrical stages. Fig. 1 shows a comparison of published receiver performances in terms of optical/electrical bandwidth and conversion gain. Because the conversion gain is the product of transimpedance gain and photodiode-responsivity, it characterizes the entire receiver OEIC and not only the preamplifier as the transimpedance gain does.

High-electron mobility transistors (HEMT's) and heterojunction bipolar transistors (HBT's) are both promising candidates to push receiver bandwidths up to 50 GHz and beyond [1], [11] (Fig. 1). In general, the high frequency noise behavior of HEMT's is better enabling potentially higher sensitivities

Manuscript received October 12, 1999; revised March 14, 2000.

D. Huber, A. Huber, T. Morf, A. Neiger, M. Rohner, I. Schnyder, V. Schwarz, and H. Jäckel are with the Electronics Laboratory, Swiss Federal Institute of Technology Zürich (ETHZ), CH-8092 Zürich, Switzerland.

M. Bitter is with the Institute of Quantum Electronics, Micro- and Optoelectronics Laboratory, CH-8093 Zürich, Switzerland.

C. Bergamaschi is with the Fachgruppe für angewandte Schaltungstechnik, CH-5210 Windisch, Switzerland.

R. Bauknecht is with Opto Speed SA, CH-6805 Mezzovico, Switzerland.

Publisher Item Identifier S 0733-8724(00)05765-0.

Fig. 1. Comparison of published optical/electrical receiver performances.

of such receivers. However, reported highest values are comparable for both technologies:  $-20.4 \text{ dBm}/-17.0 \text{ dBm}$  at 10 Gb/s/20 Gb/s for HBT-OEIC [8] and  $-17.7 \text{ dBm}/-12.0 \text{ dBm}$  at 10 Gb/s/20 Gb/s for HEMT-OEIC [12], [17], respectively. Furthermore, the minimum dimensions of HEMT's (gate width) are much smaller than the minimum emitter width of comparable HBT's leading to more relaxed lithography requirements for the HBT fabrication. And the gate threshold voltage variation of HEMT's is higher than the base-emitter voltage variation of bipolar junction transistors resulting in a more difficult bias-point control of HEMT-based circuits.

The InP–InGaAs material system in combination with a SHBT technology offers the option to use the base-collector homojunction of the transistor also for the formation of the photodiode [9]. Two advantages are the consequence of this technique: The layer structure of both devices can be grown in one step avoiding a regrowth process with its problems. In addition, the diode fabrication process can be fully incorporated into the transistor fabrication. The drawback of fabrication simplicity is a speed limiting tradeoff (collector layer thickness) between diode depletion layer capacitance and transistor transit time. However, it is the purpose of this work to show the potential of this simple approach to reach data-rates up to 80 Gb/s.

Whereas most HEMT-based receivers operating above 20 Gb/s are traveling-wave amplifiers (TWA) [11]–[15], HBT-based amplifiers are mainly lumped circuits [1]–[10], because traveling wave designs are more difficult to realize with HBT's due to the resistive small-signal behavior of their

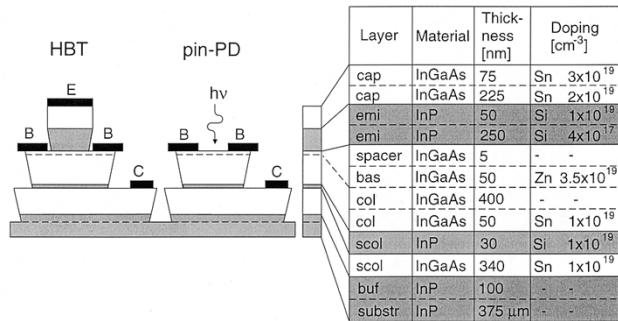

Fig. 2. Device layer structure of the InP/InGaAs SHBT and the pin-photodiode.

base emitter junction. Although reported electrical bandwidths of TWA's achieve frequencies above 100 GHz [20], best values for optical/electrical measured bandwidths are not only reached by monolithic HEMT/TWA designs [11], but also by monolithic, lumped HBT designs [1] (Fig. 1). Disadvantages of distributed circuits are their much higher chip area consumption and the fact that their reported transimpedance gains are currently around 100  $\Omega$  [11]–[15]. This is clearly lower than the corresponding gain of 170  $\Omega$  or even 380  $\Omega$  reported in [2] and in this work.

With our recent combination of the photodiode and several amplification stages resulting in a record transimpedance of 3.3 k $\Omega$  and a bandwidth of 29 GHz including a differential output we demonstrate a significant step toward a 40 Gb/s-single-chip receiver-system [7].

## II. EPITAXY

Our device layer structure is grown by metal organic vapor phase epitaxy (MOVPE).

The first layer on the semi-insulating substrate is an undoped InP buffer ( $w_{buf} = 100$  nm) needed to create a defined starting condition for the growth of the transistor (Fig. 2). Requirements for the following InGaAs subcollector layer are low sheet and contact resistances to minimize the parasitic collector series resistor. A high doping level ( $N_D = 1 \cdot 10^{19}$  cm<sup>-3</sup>) and a thickness of  $w_{scol} = 340$  nm result in a low sheet resistance value of  $R_s = 12 \Omega/\square$ .

The undoped InGaAs collector layer is not only part of the HBT but also serves as absorption region of the photodiode. Its thickness has an impact on the transistor characteristics (transit frequency, breakdown voltage, base-collector capacitance) as well as on the photodiode (transit frequency, responsivity, depletion layer capacitance). For an optimized transistor radio frequency (RF) behavior (transit frequency  $f_T = 130$  GHz, Section IV-A) a value of  $w_{col} = 400$  nm is chosen. C-V-measurements demonstrated that, due to Sn out-diffusion from the underlying subcollector layer, the depletion layer width of the collector ( $w_{dep} = 240$  nm) differs from the grown collector layer with ( $w_{col}$ ). It leads to a diode transit frequency of  $f_{T,PD} = 80$  GHz, a responsivity of  $R = 0.32$  A/W and a depletion layer capacitance of  $C_{dep} = 49$  fF (Section IV-B). For the diode, a thickness of  $w_{col} = 600$  nm would be a somewhat better compromise between  $f_{T,PD} = 65$  GHz,  $R = 0.42$  A/W and

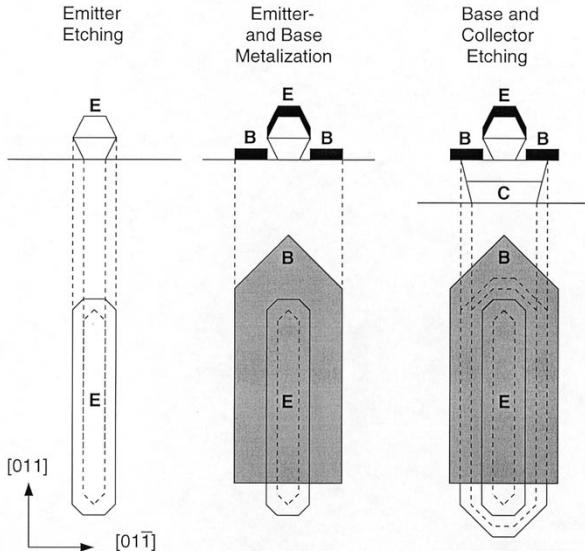

Fig. 3. Process sequences of emitter etching (left), base and emitter metallization (middle) and wet etching of base and collector employing the base metal as etching mask (right).

$C_{dep} = 27$  fF. However, the preamplifier circuit presented in Section V solves the problem of the  $RC$ -speed-limitation due to the depletion layer capacitance  $C_{dep}$ , by providing a low input impedance  $R_{IN}$ .

We use a special low-temperature growth process for a very high base Zn-doping ( $N_A = 3.5 \cdot 10^{19}$  cm<sup>-3</sup>) which has been presented in [21]. The base thickness ( $w_{bas} = 50$  nm) is a tradeoff between base sheet resistance ( $R_s = 720 \Omega/\square$ ) on one side, and base transit time along with current gain ( $\beta = 38$ ) on the other side. To overcome the well-known problem of Zn out-diffusion from base to emitter, a very thin undoped spacer layer is placed in between ( $w_{spacer} = 5$  nm). It is thick enough to inhibit the out-diffusion but thin enough to provide good base contacts.

The InP emitter also serves for the formation of a wet etched undercut providing a separation between the base- and the emitter contact metallization (Fig. 3). Therefore, its thickness ( $w_{emi} = 250$  nm) must be higher than the thickness of the first metallization layer ( $w_{pmet} = 130$  nm). To achieve a low emitter contact resistance an InGaAs cap layer is grown on the InP emitter. Cap and emitter layer together exhibit a sheet resistance of  $R_s = 7 \Omega/\square$ .

A detailed description of the epitaxy development of our device layer structure is given in [21].

## III. PROCESSING

Whereas the transit frequency  $f_T$  of the HBT is mainly determined by the vertical layer thicknesses, the maximum oscillation frequency  $f_{max}$  depends strongly on the lateral device process. Key issue of the process optimization is a reduction of the base resistance  $R_b$  and of the base-collector depletion layer capacitance  $C_{bc}$ . A large number of improvement methods for  $f_{max}$  is found in literature as for example a hexagon emitter structure [22] or the transferred substrate technology [23] which reaches the highest values for  $f_{max}$  reported to date. Our ap-

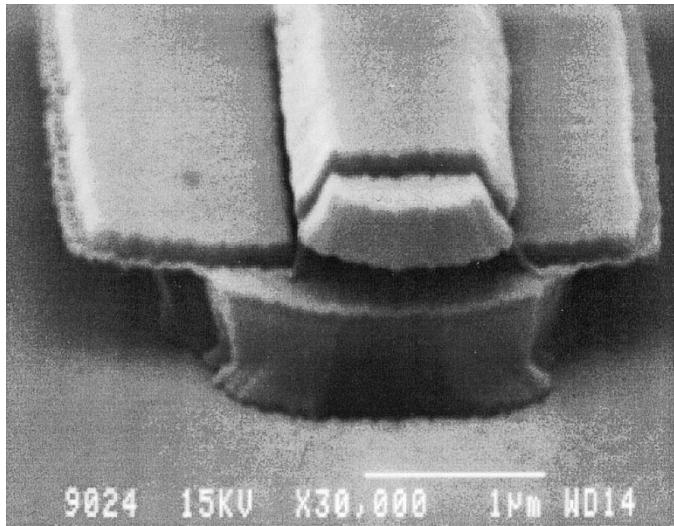

Fig. 4. HBT with an emitter geometry of  $a_e = 1.0 \times 5 \mu\text{m}^2$  after the wet etching of the base and collector layers employing the base metal as an etching mask.

proach is based on an emitter overhang for a self-aligned separation of base- and emitter contacts and of a base-metal undercut for the minimization of  $C_{bc}$ . The process is self-aligned for all critical steps allowing smallest emitter-widths of  $0.5 \mu\text{m}$  using an optical lithography 2-in wafer technology.

The first process step is the emitter formation by a wet etching of the emitter cap (InGaAs) and of the InP emitter. As mentioned in Section II, the InP emitter is thick enough to provide a sufficient overhang (Fig. 3 left) for the self-aligned evaporation of the emitter- and base contacts (Fig. 3 middle). The metal layer evaporation sequence is Pt/Ti/Pt/Au. For contact improvement we perform an annealing ( $430^\circ\text{C}/1 \text{ min}$ ) resulting in specific contact resistances of  $\rho_{bas} = 3.5 \cdot 10^{-7} \Omega \text{ cm}^2$  for the base p-contact and of  $\rho_{emi} = 1.5 \cdot 10^{-7} \Omega \text{ cm}^2$  for the emitter n-contact, respectively. These results agree well with the lowest values found in literature [22], [24].

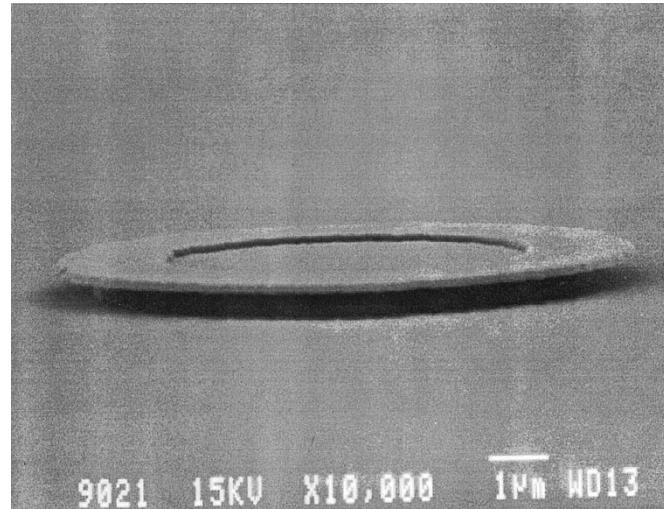

The base metal is used then as an etching mask for the base- and the collector wet etching, resulting in a base metal undercut for a reduced parasitic base-collector depletion capacitance (Fig. 3 right, Fig. 4). This method of metal undercut is also applied for the fabrication of the photodiode (Fig. 5) resulting in an undercut of  $\Delta r_{cut} \approx 1 \mu\text{m}$  and in a diameter of the depletion layer of  $d_{dep} = 11 \mu\text{m}$  for a circular photodiode with a diameter of the light active region of  $d_{pin} = 9 \mu\text{m}$ . Compared to a conventional detector (no undercut,  $d_{pin} = 9 \mu\text{m}$ ) the total parasitic capacitance ( $C_{par}$ ) is reduced by 30% (from 89 fF to 62 fF) without loss of light sensitive area.

Subsequent evaporation of a layer sequence of Ti/Pt/Au forms the collector contact (Specific contact resistance:  $\rho_{col} = 3.4 \cdot 10^{-7} \Omega \text{ cm}^2$ ). Furthermore, device isolation is performed by a wet chemical removal of the subcollector and the following passivation consists of a thick polyimide layer ( $4.5 \mu\text{m}$ ) for good planarization.

By unmasked dry etching we can remove the polyimide until the emitter mesa break through the polyimide surface: Self-aligned emitter contacts are created and only the less critical via holes for the base and the collector contacts remain to be gen-

Fig. 5. Photodiode with a diameter of the light active area of  $d_{pin} = 6 \mu\text{m}$ . The wet etched undercut of the p-contact metallization is  $\Delta r_{cut} \approx 1 \mu\text{m}$ .

TABLE I

DEPENDENCE OF THE SMALL-SIGNAL CURRENT-GAIN  $\beta$  ON THE

EMITTER-WIDTH  $b_e$

| $b_e [\mu\text{m}]$ : | 0.5 | 0.7 | 1.0 | 1.5 | 2.5 |

|-----------------------|-----|-----|-----|-----|-----|

| $\beta$ :             | 20  | 29  | 38  | 46  | 58  |

erated by masked dry etching. The range of emitter widths covered by our process is:  $0.5 \mu\text{m} \leq b_e \leq 2.5 \mu\text{m}$ . Due to surface recombination effects the small-signal current-gain  $\beta$  depends strongly on the emitter-width  $b_e$  as shown in Table I.

Highest values for the maximum oscillation frequency ( $f_{max} = 240 \text{ GHz}$ ) were reached by transistors with an emitter area of  $a_e = 1.0 \times 8 \mu\text{m}^2$ . A scaling of the emitter-width reduces only the intrinsic resistance  $R_b$  and the intrinsic capacitance  $C_{bc}$  keeping the extrinsic parasitics constant which leads to an optimal width of  $b_e = 1.0 \mu\text{m}$  for the highest  $f_{max}$ .

The process comprises also thin-film Cr-resistors with a sheet resistance of  $50 \Omega/\square$ , metal-insulator-metal (MIM) capacitors formed by evaporation of  $Ta_2O_5$  ( $w_{tantal} = 500 \text{ nm}$ ), and a final  $\text{SiO}/\text{Al}_2\text{O}_3$  double layer antireflection coating to reduce optical coupling losses.

#### IV. DEVICE CHARACTERIZATION

##### A. Transistor

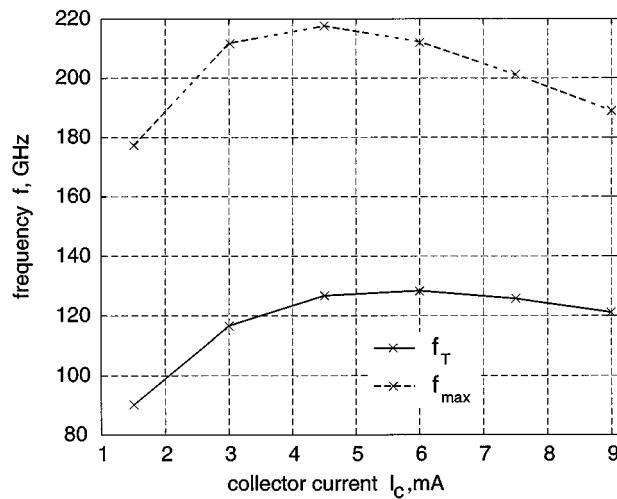

In all circuits presented here, we use transistors with an emitter geometry of  $a_e = 1.0 \times 5 \mu\text{m}^2$ . They reach an optimal RF performance at collector currents in the range of  $3 \text{ mA} \leq I_c \leq 7 \text{ mA}$  (Fig. 6). Additionally, they exhibit a dc-current-gain of  $\beta = 38$ , a breakdown voltage of  $BV_{ce0} = 6 \text{ V}$ , a transit frequency of  $f_T = 130 \text{ GHz}$  at a collector-emitter voltage of  $V_{ce} = 1.5 \text{ V}$  and a maximum oscillation frequency of  $f_{max} = 220 \text{ GHz}$  at  $V_{ce} = 2 \text{ V}$  (Fig. 6).

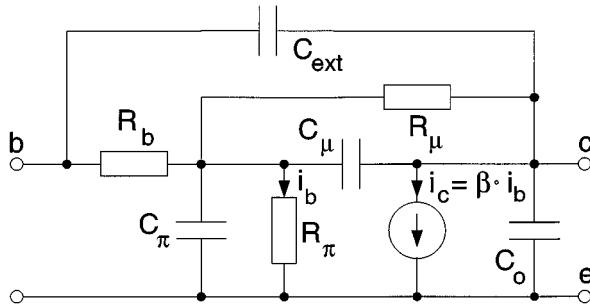

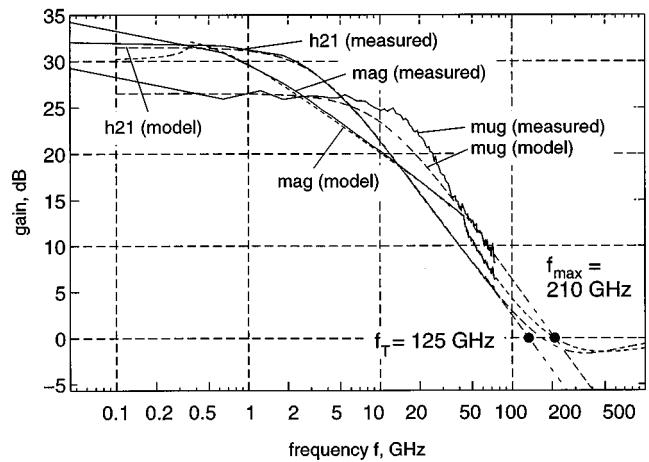

We employ a hybrid  $\pi$ -model as small-signal equivalent circuit for the description of the transistor (Fig. 7). A fit of the model to the measured S-parameter (Bias condition:  $I_c = 6 \text{ mA}$ ;  $V_{ce} = 2 \text{ V}$ ) leads to the model parameters given in Table II. A comparison of the frequency dependencies of the transistor

Fig. 6. Figure of merits in terms of  $f_T$  and  $f_{\max}$  versus the collector current  $I_c$  of a transistor with an emitter area of  $a_e = 1.0 \times 5 \mu\text{m}^2$  at a collector-emitter voltage of  $V_{ce} = 2$  V.

Fig. 7. Small-signal equivalent circuit of the HBT.

model with the measured data in terms of mason unilateral gain (mug), maximum available gain (mag) and small-signal current-gain (h21) shows excellent agreement over the full frequency range of  $45 \text{ MHz} \leq f \leq 75 \text{ GHz}$  (Fig. 8). Therefore, we use this model for the extraction of the maximum oscillation frequency and of the transit frequency. The transit time for the presented model parameters is calculated as

$$\tau_T = \frac{1}{\omega_T} = \tau_b + \tau_c + \tau_{bc,int} + \tau_{bc,ext} = 1.28 \text{ ps.} \quad (1)$$

The individual contributions are

$$\tau_b + \tau_c = \frac{R_\pi}{\beta} C_\pi = 1.14 \text{ ps} \quad (2)$$

$$\tau_{bc,int} = \frac{R_\pi}{\beta} C_\mu = 0.04 \text{ ps} \quad (3)$$

$$\tau_{bc,ext} = \frac{R_\pi + R_b}{\beta} C_{ext} = 0.10 \text{ ps.} \quad (4)$$

Obviously the base- and the collector-delay (1.14 ps) dominate over the contributions of the base-collector capacitances (0.14 ps).

TABLE II

PARAMETERS OF THE SMALL-SIGNAL EQUIVALENT CIRCUIT OF A TRANSISTOR

HAVING AN Emitter AREA OF  $a_e = 1.0 \times 5 \mu\text{m}^2$  AT BIAS CONDITION

$V_{ce} = 2$  V AND  $I_c = 6$  mA

| $\beta$ | $R_b$       | $R_\pi$      | $R_\mu$              | $C_\pi$         | $C_\mu$          | $C_{ext}$        | $C_0$          |

|---------|-------------|--------------|----------------------|-----------------|------------------|------------------|----------------|

| 38      | $45 \Omega$ | $601 \Omega$ | $31 \text{ k}\Omega$ | $72 \text{ fF}$ | $2.7 \text{ fF}$ | $6.6 \text{ fF}$ | $2 \text{ fF}$ |

Fig. 8. Comparison of the RF-performance of a transistor with emitter area of  $a_e = 1.0 \times 5 \mu\text{m}^2$  (Bias condition:  $V_{ce} = 2$  V;  $I_c = 6$  mA) with the small-signal model having the values presented in Table II. mug: Mason unilateral gain. mag: Maximum available gain. h21: Small-signal current-gain.

### B. Photodiode

Base-, collector- and subcollector layer of our HBT-structure form the photodiode. As mentioned in Section II, the nonoptimal collector layer thickness (400 nm instead of optimal 600 nm) causes a relatively low responsivity  $R_{dc}$  and a higher than optimal depletion layer capacitance  $C_{dep}$ . A diameter of the light active area of  $d_{pin} = 9 \mu\text{m}$  is chosen as compromise between a reasonable optical coupling and a sufficient low depletion layer capacitance. However, with the undercut of the p-contact (Fig. 5) described in Section III, this tradeoff is significantly relaxed.

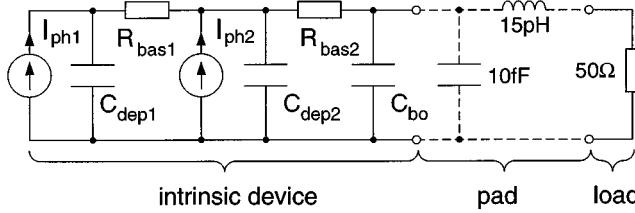

The RF-model of the photodiode is shown in Fig. 9. Two segments ( $I_{ph1,2}$ ,  $C_{dep1,2}$ ,  $R_{bas1,2}$ ) are employed to model the distributed effects of the pin-structure. We choose the inner segment to be 25% of the total absorption area, with the consequence for the relation of the two photocurrents and of the two depletion layer capacitances:  $C_{dep1} : C_{dep2} = I_{ph1} : I_{ph2} = 1 : 3$ . From electrical one-port-S-parameter measurements, we extracted the depletion layer capacitance:  $C_{dep} = C_{dep1} + C_{dep2} = 49 \text{ fF}$ . Measurements of photodiodes with different diameters allowed the discrimination between the depletion layer capacitance ( $C_{dep}$ ) and the stray capacitance ( $C_{bo}$ ). Values for the elements of the intrinsic device are summarized in Table III. Relatively high resistor values are shown, which are due to the high sheet resistance ( $R_s = 720 \Omega/\square$ ) of the thin base layer. Saturation velocities of holes and electrons in the depleted absorption region [25] as well as hole-diffusion in the non depleted absorption region [26] limit the photodiode transit frequency to  $f_{T,Pin} = 80 \text{ GHz}$ . This frequency dependence is taken into account as a low-pass characteristics of the photocurrent source,

Fig. 9. 2-segment RF-model of the pin-diode.

TABLE III

PARAMETERS OF THE RF-MODEL OF THE PIN-DIODE

| $R_{bas1}$ | $R_{bas2}$ | $C_{dep1}$ | $C_{dep2}$ | $C_{bo}$ |

|------------|------------|------------|------------|----------|

| 200Ω       | 6.5Ω       | 12.3fF     | 36.8fF     | 13fF     |

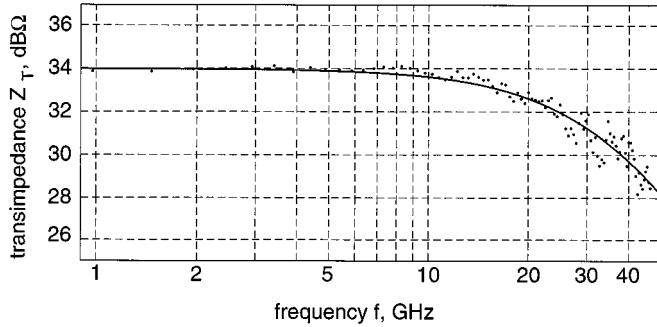

Fig. 10. Comparison of the transimpedance gain of the photodiode model (solid line) with the measured, Fourier-transformed and corrected pulse response of the photodiode (dots).

with  $P_{opt}$  being the power of the incident light and  $R_{dc}$  the responsivity of the detector

$$I_{ph} = I_{ph1} + I_{ph2} = P_{opt} \cdot R_{dc} \cdot \frac{1}{1 + j \frac{f}{f_{T\text{pin}}}}. \quad (5)$$

Optical/electrical on-wafer characterization was carried out at the wavelength  $\lambda = 1550$  nm using a lensed single-mode fiber probe for top illumination. Pulse response measurements were performed with a pulsed mode locked laser (Ti:Sa-laser and OPO for  $\lambda = 1550$  nm, pulsed width:  $\tau_p < 1$  ps) and a sampling scope (rise time: 7 ps) [27]. Fourier-transform and deconvolution of the measurement setup (cable, bias tee and sampling head) in frequency domain reveals the optical/electrical frequency response of the photodiode. A comparison of the measured and the calculated frequency response shows good accordance (Fig. 10). Since the input impedance of the measurement system is 50 Ω the  $-3$  dB-bandwidth reaches only values of  $f_{-3\text{ dB}} = 31$  GHz (pads included) and of  $f_{-3\text{ dB}} = 33$  GHz (pads excluded) due to the RC-limitation of the total parasitic capacitance and the 50 Ω-load. A dc responsivity of  $R_{dc} = 0.32$  A/W and a dark current of  $I_{dark} < 2$  nA were measured at a reverse bias voltage of  $V_{rev} = 3$  V.

## V. CIRCUIT DESIGN

To increase the RC-limited bandwidth of the detector ( $f_{-3\text{ dB}} = 33$  GHz) to the much higher bandwidth of the entire

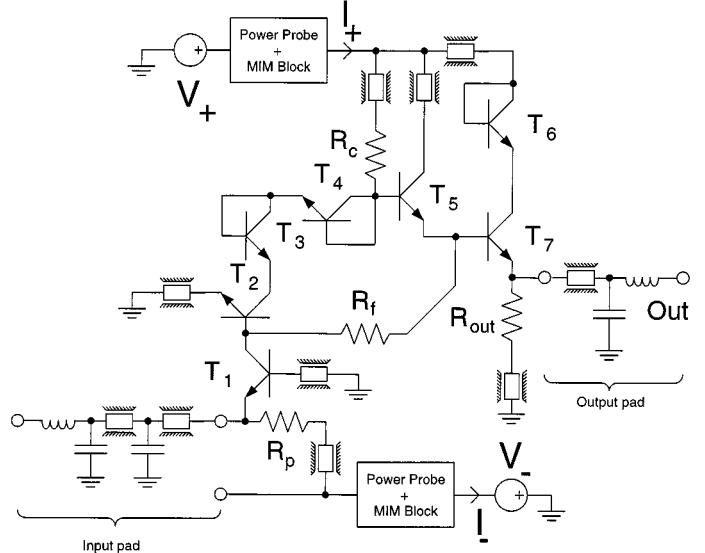

Fig. 11. Circuit-schematics including parasitics of interconnections, signal pads and power probes.

TABLE IV

COMPARISON OF CIRCUIT VERSIONS

| $f_{-3\text{ dB}}$ | $C_{par}$ | $Z_T$ | $R_p$ | $R_f$ | $R_c$ | $R_{out}$ |

|--------------------|-----------|-------|-------|-------|-------|-----------|

| 34 GHz             | 62 fF     | 380 Ω | 750 Ω | 600 Ω | 350 Ω | 250 Ω     |

| 50 GHz             | 62 fF     | 170 Ω | 380 Ω | 310 Ω | 120 Ω | 250 Ω     |

| 60 GHz             | 31 fF     | 130 Ω | 380 Ω | 230 Ω | 125 Ω | 250 Ω     |

receiver ( $f_{-3\text{ dB}} = 50$  GHz), a very low input impedance of the preamplifier is essential. As a consequence, we choose a common base input stage (Fig. 11,  $T_1$ ) providing an input impedance of ( $Z_{IN} = 15$  Ω) at low frequencies. The gain stage is a transimpedance amplifier ( $T_2 - T_5$ ) followed by a common collector output stage ( $T_6, T_7$ ) for optimal driving capability [28]. This circuit is meant to be connected monolithically to the next gain stage (as demonstrated in [7]), and hence a 50-Ω-matching is unnecessary. Nevertheless, the circuit has to be measured in a 50-Ω system.

Transimpedance gain can be traded for bandwidth by a simple adjustment of mainly two resistor values ( $R_c, R_f$ ). Three versions for the bandwidths of 34, 50, and 60 GHz were designed. Whereas the circuits achieving 34 and 50 GHz were fabricated and characterized, the fastest version is a simulation to demonstrate the potential for reaching a bit rate of 80 Gb/s. The 60 GHz predicted can only be achieved by an additional reduction of the pin-diode diameter to 6  $\mu\text{m}$  resulting in a total parasitic capacitance of  $C_{par} = 31$  fF. Table IV presents the differences between the three versions.

For bias-point considerations, we used the Gummel-Poon dc transistor model. Nominal supply voltages were  $V_+ = 5$  V and  $V_- = -3.8$  V and the corresponding currents  $I_+ = 22$  mA and  $I_- = -6$  mA. All collector currents are in the range of  $4$  mA  $< I_C < 7$  mA for optimal high speed operation (Fig. 6).

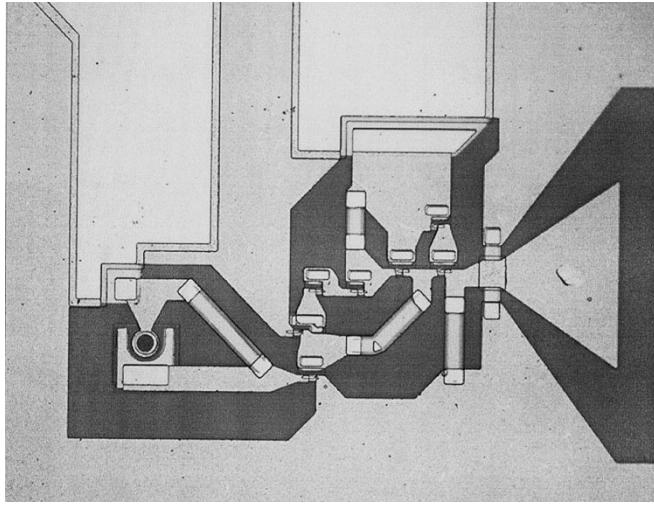

Three different layouts have been designed for each circuit version: 1) The complete OEIC layout (containing photodiode and preamplifier, Fig. 12) for optical/electrical characterization, 2) the preamplifier layout (photodiode replaced by an input pad,

Fig. 12. Photograph of the 50-GHz receiver showing the photodiode on the left and the coplanar output on the right.

Fig. 11) for electrical characterization, and 3) a layout consisting of the power probe pads and the supply blocking capacitors to characterize the power supply separately. AC-simulations up to 60 GHz were made using measured and deembedded S-parameter files of the transistors (Fig. 11) as well as one-port files containing the power supply data. Parasitics of pads and interconnections cannot be neglected at these high frequencies and are modeled as waveguides, capacitors and inductors respectively. Especially the distributed effects of the ground connections of the transistors  $T_1$  and  $T_2$  cause a slight inductive peaking, which had to be taken into account in the design. Thus, a decrease of 8 GHz (15%) in bandwidth occurs by simulation of the circuit without considering these parasitics. For the simulation of the system consisting of photodiode and preamplifier, the equivalent circuit of the input pad in Fig. 11 was replaced by the ac-model of the photodiode shown in Fig. 9.

For the reason that a setup for bit error ratio (BER) measurements at 40 Gb/s is presently not available, we calculate a sensitivity based on a noise analysis of our preamplifier topology. The noise model of the transistor includes three sources: Thermal noise of the base resistance  $R_b$  (Table II) and shot noise of the base- and of the collector current. We identified four major parts dominating the total equivalent input noise current of the circuit: Current noise of the resistors  $R_p$  (16%) and  $R_f$  (23%) and shot noise contributions of the base currents of the transistors  $T_1$  (23%) and  $T_2$  (26%). Based on the calculated average equivalent input noise current density ( $i_{\text{neq}} = 16.2 \text{ pA}/\sqrt{\text{Hz}}$ ) and using the  $Q$ -method ( $Q = 6$ ) [29], the sensitivity for a bit error ratio of  $\text{BER} = 10^{-9}$  at 40 Gb/s becomes

$$\overline{P}_{\text{opt}} = \frac{2Q\sqrt{i_{\text{neq}}^2 f_n}}{2R_{\text{dc}}} = -11.8 \text{ dBm.} \quad (6)$$

For this calculation we suppose the noise-free detection system to have a first-order low-pass characteristics with a bandwidth of  $f_{-3 \text{ dB}} = 30 \text{ GHz}$ . Then, the corresponding noise bandwidth is  $f_n = (\pi/2) \cdot f_{-3 \text{ dB}} = 47 \text{ GHz}$ .

Fig. 13. Transimpedance of the 50 GHz-preamplifier. Dashed line: Simulation. Solid line: Measurement.

## VI. RECEIVER CHARACTERIZATION

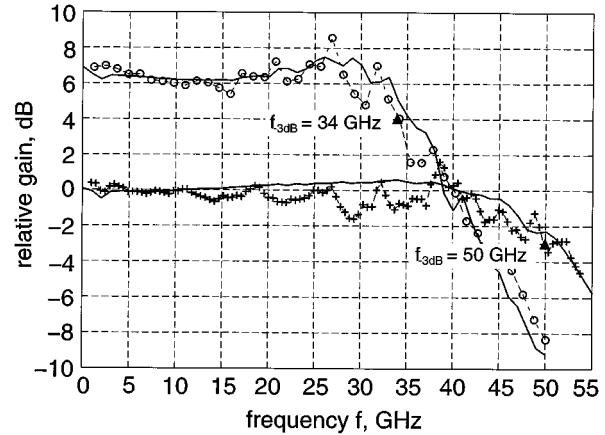

This section presents the on-wafer characterization of the receiver OEIC's and comparisons between measurements and simulations. Whereas the mentioned comparisons concern the 50-GHz receiver, only the most important measurement results being optical/electrical frequency response, 40-Gb/s eye pattern and sensitivity are presented for the version reaching 34 GHz.

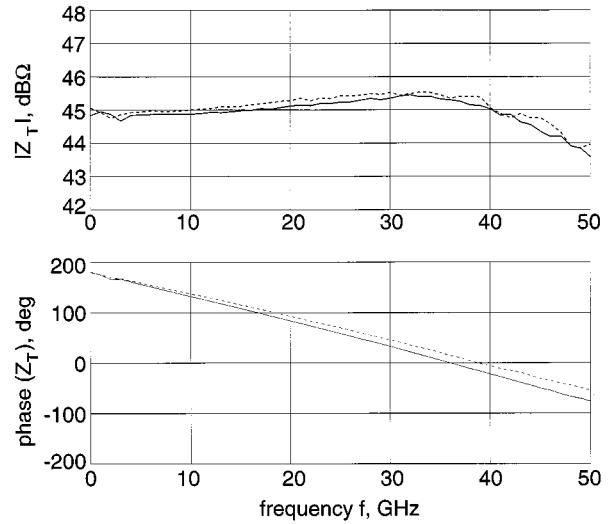

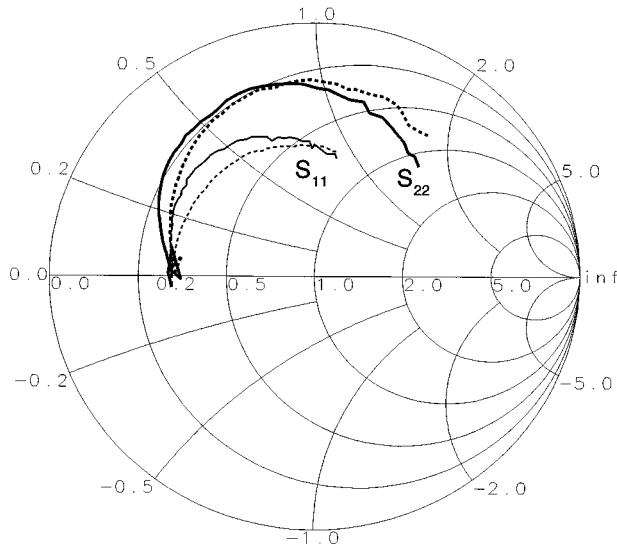

Fig. 13 shows a comparison of the transimpedance derived from electrical S-parameter measurements with the simulated transimpedance of the circuit shown in Fig. 11. Good agreement between measurement and simulation is found. The dc transimpedance of the amplifier is  $Z_T = 170 \Omega$  (34-GHz receiver:  $Z_T = 380 \Omega$ ) and the bandwidth is  $f_{-3 \text{ dB}} > 50 \text{ GHz}$ . In addition, linear phase characteristics up to 50 GHz are demonstrated. Fig. 14 presents input and output reflection coefficients of the preamplifier. A dc input impedance of  $Z_{IN} = 15 \Omega$  is achieved and the magnitude of the de-embedded input impedance (without equivalent circuit of the input pad) is below  $22 \Omega$  over the full frequency range up to 50 GHz. As mentioned in Section V the output impedance is not matched to  $50 \Omega$  (Fig. 14). With a series resistor in the output a matching could be achieved at the cost of a reduced transimpedance gain.

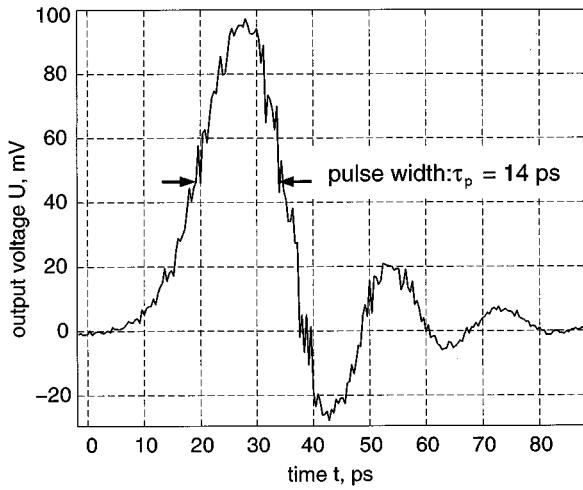

Optical/electrical pulse response measurements with the setup described in Section IV-B and [27] result in a pulsewidth of the receiver of  $\tau_p = 14 \text{ ps}$  (34-GHz receiver:  $\tau_p = 16.5 \text{ ps}$ ) (Fig. 15). An oscillation in the pulse response is observed. Assuming the transfer function of the receiver to be a second-order low-pass filter, this oscillations can be calculated to result in a peaking of the frequency response of  $\Delta Z_T \approx 1 \text{ dB}$ , which is in accordance with the results presented in Fig. 16. Because we are not equipped for a time domain characterization of our measurement setup (cable, bias tee and sampling head), the impulse response is not deconvolved. By Fourier transform and correction of the measurement setup in frequency domain, we obtained the optical/electrical frequency responses of the receiver OEIC's as depicted in Fig. 16. A bandwidth of

Fig. 14. Input and output reflection coefficients of the 50 GHz-preamplifier in the frequency range of  $45 \text{ MHz} \leq f \leq 50 \text{ GHz}$ . Dashed line: Simulation. Solid line: Measurement.

Fig. 15. Optical/electrical impulse response of the 50-GHz receiver (rise time of measurement setup included).

$f_{-3 \text{ dB}} = 50 \text{ GHz}$  is achieved ( $f_{-3 \text{ dB}} = 34 \text{ GHz}$  for the receiver with higher gain).

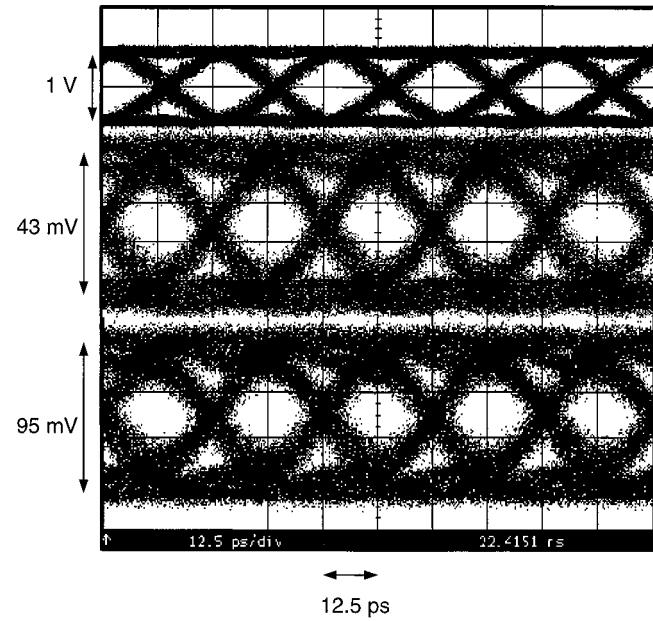

Measurements of the optical/electrical eye-pattern at 40 Gb/s were performed using a 10-Gb/s pattern generator, a 4:1 multiplexer, a driving amplifier and an optical modulator. Clear eye pattern for the 34 GHz- and for the 50 GHz receiver are obtained although the speed limiting factor in this measurement chain is the optical modulator with a bandwidth of  $f_{-3 \text{ dB}} = 23 \text{ GHz}$ . (Fig. 17).

As mentioned in Section V a setup for BER-measurements at 40 Gb/s was not available. Therefore, we support our sensitivity calculations for 40 Gb/s with BER-measurements at 10 Gb/s [nonreturn-to-zero (NRZ)  $2^{15} - 1$  pseudorandom binary sequence (PRBS)]. We assume a first-order low-pass characteristics of the postamplifier (measured bandwidth:  $f_{-3 \text{ dB}} = 11$

Fig. 16. Optical/electrical frequency responses of the receivers. Solid lines: Simulated frequency responses. Dashed line with crosses: Measured, Fourier transformed and corrected impulse response (50-GHz receiver). Dashed line with circles: Measured, Fourier transformed, and corrected impulse response (34-GHz receiver).

Fig. 17. Optical/electrical eye-pattern at 40 Gb/s and a NRZ  $2^{31} - 1$  prbs. Upper trace: input signal of the modulator driver. Middle trace: Output signal of the 50-GHz receiver. Lower trace: Output signal of the 34 GHz receiver. Average photocurrent:  $\bar{I}_{\text{ph}} \approx 120 \mu\text{A}$ .

GHz) between receiver output and error detector input. Then the noise bandwidth is  $f_n = (\pi/2) \cdot f_{-3 \text{ dB}} = 17 \text{ GHz}$  and a calculated sensitivity of  $-14.0 \text{ dBm}$  should be achieved (6). The measured value is  $\bar{P}_{\text{opt}} = -10.7 \text{ dBm}$  (including the noise contribution of the postamplifier). A correction of this result by eliminating the postamplifier's additional noise (minimum noise figure:  $F_{\text{min}} > 4 \text{ dB}$ ) leads to  $\bar{P}_{\text{opt}} < -12.7 \text{ dBm}$ , resulting in a slight difference of approximately 1 dBm.

Furthermore, we measured a better sensitivity for the 34-GHz receiver of  $\bar{P}_{\text{opt}} = -12.7 \text{ dBm}$  (noise of the postamplifier included) due to lower transistor bias currents and higher resistor values.

## VII. SUMMARY

In this paper we demonstrate receiver front ends fabricated with a simple technology avoiding sub-micron lithography and multi-step epitaxy. Measurement results of realized circuits are transimpedance gains of  $Z_T = 170 \Omega$  and  $Z_T = 380 \Omega$  along with optical/electrical bandwidths of  $f_{-3 \text{ dB}} = 50 \text{ GHz}$  and  $f_{-3 \text{ dB}} = 34 \text{ GHz}$ . To the best of our knowledge, these results are the highest transimpedance gain ( $380 \Omega$ ) in the frequency range above 30 GHz and the highest optical/electrical bandwidth (50 GHz) of any HBT-based receiver OEIC reported to date. By means of simulation, we show that, by a further reduction of the feedback resistor and of the photodiode diameter, an optical/electrical bandwidth of 60 GHz can be reached, enabling future bitrates up to 80 Gb/s.

## ACKNOWLEDGMENT

The authors would like to thank Dr. V. Hurm, M. Ludwig, and Dr. M. Schlechtweg from Fraunhofer Institute in Freiburg, Germany, for performing 40 Gb/s eye-pattern measurements, Dr. E. Gini for the epitaxial work, H. R. Benedickter for support in high-frequency characterization, and R. Schreieck for support in optical/electrical pulse measurements.

## REFERENCES

- [1] D. Huber, M. Bitter, E. Gini, A. Neiger, T. Morf, C. Bergamaschi, and H. Jäckel, "50 GHz monolithically integrated InP/InGaAs PIN/HBT receiver," in *Proc. 11th Conf. Indium Phosphide and Related Mater.*, May 1999, pp. 6–7.

- [2] D. Huber, M. Bitter, T. Morf, C. Bergamaschi, H. Melchior, and H. Jäckel, "46 GHz bandwidth monolithic InP/InGaAs PIN/SHBT photoreceiver," *Electron. Lett.*, vol. 35, no. 1, pp. 40–41, Jan. 1999.

- [3] D. Huber, M. Bitter, S. Romier, I. Schnyder, R. Bauknecht, T. Morf, C. Bergamaschi, and H. Jäckel, "23 GHz monolithically integrated InP/InGaAs PIN/HBT receiver with  $12 \text{ THz} \Omega$  gain-bandwidth product," in *Proc. 10th Conf. Indium Phosphide and Related Mater.*, May 1998, pp. 447–450.

- [4] M. Bitter, R. Bauknecht, W. Hunziker, and H. Melchior, "Monolithically integrated 40-Gb/s InP/InGaAs PIN/HBT optical receiver module," in *Proc. 11th Conf. Indium Phosphide and Related Mater.*, May 1999, pp. 381–384.

- [5] U. Westergren, D. Haga, and B. Willen, "Monolithic optoelectronic receivers with up to 24 GHz bandwidth using InP pin-HBT technology," in *Proc. 23th Eur. Conf. Optical Commun.*, vol. 4, Sept. 1997, pp. 105–108.

- [6] E. Sano, M. Yoneyama, S. Yamahata, and Y. Matsuoka, "InP/InGaAs double-heterojunction bipolar transistors for high-speed optical receivers," *IEEE Trans. Electron Devices*, vol. 43, pp. 1826–1832, Nov. 1996.

- [7] A. Huber, D. Huber, T. Morf, C. Bergamaschi, V. Hurm, M. Ludwig, M. Schlechtweg, and H. Jäckel, "Monolithic high transimpedance gain (3.3 k $\Omega$ ), 40 Gb/s InP-HBT photoreceiver with differential outputs," *Electron. Lett.*, vol. 35, no. 11, pp. 897–898, May 1999.

- [8] L. M. Lunardi, S. Chandrasekhar, A. H. Gnauck, C. A. Burrus, and R. A. Hamm, "20-Gb/s monolithic p-i-n/HBT photoreceiver module for 1.55- $\mu\text{m}$  applications," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 1201–1203, Oct. 1995.

- [9] S. Chandrasekhar, L. M. Lunardi, A. H. Gnauck, R. A. Hamm, and G. J. Qua, "High-speed monolithic p-i-n/HBT and HPT/HBT photoreceivers implemented with simple phototransistor structure," *IEEE Photon. Technol. Lett.*, vol. 5, pp. 1316–1318, Nov. 1993.

- [10] E. Sano, K. Sano, T. Otsuji, K. Kurishima, and S. Yamahata, "Ultra-high speed, low power monolithic photoreceiver using InP/InGaAs double-heterojunction bipolar transistors," *Electron. Lett.*, vol. 33, no. 12, pp. 1047–1048, June 1997.

- [11] K. Takahata, Y. Muramoto, H. Fukano, and Y. Matsuoka, "52 GHz bandwidth monolithically integrated WGPD/HEMT photoreceiver with large O/E conversion factor of 105 V/W," *Electron. Lett.*, vol. 35, no. 19, pp. 1639–1640, Sept. 1999.

- [12] K. Takahata, Y. Muramoto, H. Fukano, K. Kato, A. Kozen, O. Nakajima, and Y. Matsuoka, "46.5-GHz-bandwidth monolithic receiver OEIC consisting of a waveguide PIN photodiode and a HEMT distributed amplifier," *IEEE Photon. Technol. Lett.*, vol. 10, pp. 1150–1152, Aug. 1998.

- [13] Y. Miyamoto, M. Yoneyama, Y. Imai, K. Kato, and H. Tsunetsugu, "40 Gb/s optical receiver module using a flip-chip bonding technique for device interconnection," *Electron. Lett.*, vol. 34, no. 5, pp. 493–494, Mar. 1998.

- [14] V. Hurm, W. Benz, W. Bronner, A. Hülsmann, T. Jakobus, K. Köhler, A. Leven, M. Ludwig, B. Raynor, J. Rosenzweig, M. Schlechtweg, and A. Thiede, "40 Gb/s 1.55  $\mu\text{m}$  pin-HEMT photoreceiver monolithically integrated on 3 in GaAs substrate," *Electron. Lett.*, vol. 34, no. 21, pp. 2060–2062, Oct. 1998.

- [15] G. Mekonnen, W. Schlaak, H.-G. Bach, R. Steingrüber, A. Seeger, Th. Engel, W. Passenberg, A. Umbach, C. Schramm, G. Unberbisch, and S. van Waasen, "37-GHz bandwidth InP-based photoreceiver OEIC suitable for data rates up to 50 Gb/s," *IEEE Photon. Technol. Lett.*, vol. 11, pp. 257–259, Feb. 1999.

- [16] B. Klepser, J. Spicher, C. Bergamaschi, W. Patrick, and W. Bächtold, "High speed, monolithically integrated pin-HEMT photoreceiver fabricated on InP with a tunable bandwidth up to 22 GHz using a novel circuit design," in *Proc. 8th Conf. Indium Phosphide and Related Mater.*, May 1996, pp. 443–446.

- [17] P. Fay, I. Adesida, C. Caneau, and S. Chandrasekhar, "High sensitivity monolithically integrated PIN-HEMT photoreceivers," in *Proc. 10th Conf. Indium Phosphide and Related Mater.*, May 1998, pp. 439–442.

- [18] Z. Lao, V. Hurm, A. Thiede, M. Berroth, M. Ludwig, H. Lienhart, M. Schlechtweg, J. Hornung, W. Bronner, K. Köhler, A. Hülsmann, G. Kaufel, and Th. Jakobus, "Modulator driver and photoreceiver for 20 Gb/s optic-fiber links," *J. Lightwave Technol.*, vol. 16, pp. 1491–1497, Aug. 1998.

- [19] V. Hurm, W. Benz, W. Bronner, T. Fink, G. Kaufel, K. Köhler, Z. Lao, M. Ludwig, B. Raynor, J. Rosenzweig, M. Schlechtweg, and J. Windscheif, "20 Gb/s long wavelength monolithic integrated photoreceiver grown on GaAs," *Electron. Lett.*, vol. 33, no. 7, pp. 624–626, Mar. 1997.

- [20] B. Agarwal, A. E. Schmitz, J. J. Brown, M. Matloubian, M. G. Case, M. Le, M. Lui, and M. J. W. Rodwell, "112 GHz, 157 GHz, and 180 GHz InP HEMT traveling-wave amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 2553–2559, Dec. 1998.

- [21] R. Bauknecht, "InP double heterojunction bipolar transistors for driver circuits in fiber optical communication systems," Ph.D. dissertation ETH Nr. 12 455, Dec. 1997.

- [22] S. Yamahata, K. Kurishima, H. Ito, and Y. Matsuoka, "Over-220-GHz- $f_T$ -and- $f_{\text{max}}$  InP/InGaAs double-heterojunction bipolar transistors with a new hexagonal-shaped emitter," in *Proc. GaAs IC Symp.*, 1995, pp. 163–165.

- [23] Q. Lee, B. Agarwal, D. Mensa, R. Pulela, J. Guthrie, L. Samoka, and M. J. W. Rodwell, "A > 400 GHz  $f_{\text{max}}$  transferred-substrate heterojunction bipolar transistor IC technology," *IEEE Electron Device Lett.*, vol. 19, pp. 77–79, Mar. 1998.

- [24] L. G. Shantarama2, H. Schuhmacher, H. P. Leblanc, R. Esagui, R. Bhat, and M. Koza, "Evaluation of single ohmic metallizations for contacting both *p*- and *n*-type GaInAs," *Electron. Lett.*, vol. 26, no. 15, pp. 1127–1129, July 1990.

- [25] G. Lucovsky, R. Schwarz, and R. Emmons, "Transit time considerations in pin-diodes," *J. Appl. Phys.*, vol. 35, no. 3, pp. 622–627, Mar. 1964.

- [26] D. E. Sawyer and R. H. Rediker, "Narrow basew Germanium photodiodes," *Proc. IRE*, vol. 46, no. 6, pp. 1122–1130, June 1958.

- [27] P. A. Schulz and K. L. Hall, "Impulse response measurements with 50-GHz bandwidth," *IEEE Microwave Guided Wave Lett.*, vol. 9, pp. 120–122, Mar. 1999.

- [28] T. Vanisri and C. Toumazou, "Integrated high frequency low noise current-mode optical transimpedance preamplifiers," *IEEE J. Solid State Circuits*, vol. 30, pp. 677–685, June 1995.

- [29] G. P. Agrawal, *Fiber-Optic Communication Systems*. New York: Wiley, 1997, pp. 165–166.

**D. Huber**, photograph and biography not available at the time of publication.

**R. Bauknecht**, photograph and biography not available at the time of publication.

**C. Bergamaschi**, photograph and biography not available at the time of publication.

**A. Neiger**, photograph and biography not available at the time of publication.

**M. Bitter**, photograph and biography not available at the time of publication.

**M. Rohner**, photograph and biography not available at the time of publication.

**A. Huber**, photograph and biography not available at the time of publication.

**I. Schnyder**, photograph and biography not available at the time of publication.

**T. Morf**, photograph and biography not available at the time of publication.

wording needed.

**V. Schwarz**, photograph and biography not available at the time of publication.

**H. Jäckel**, photograph and biography not available at the time of publication.