# Monolithically Integrated Multichannel SiGe/Si p-i-n-HBT Photoreceiver Arrays

Omar Qasaimeh, Zhenqiang Ma, *Student Member, IEEE*, Pallab Bhattacharya, *Fellow, IEEE*, and Edward T. Croke

**Abstract**—A low-power, short-wavelength eight-channel monolithically integrated photoreceiver array, based on SiGe/Si heterojunction bipolar transistors, is demonstrated. The photoreceiver consists of a photodiode, three-stage transimpedance amplifier, and passive elements for feedback, biasing and impedance matching. The photodiode and transistors are grown by molecular beam epitaxy in a single step. The p-i-n photodiode exhibits a responsivity of  $0.3\text{A/W}$  and a bandwidth of  $0.8\text{ GHz}$  at  $\lambda = 0.88\text{ }\mu\text{m}$ . The three-stage transimpedance amplifier demonstrates a transimpedance gain of  $43\text{ dB}\Omega$  and a  $-3\text{ dB}$  bandwidth of  $5.5\text{ GHz}$ . A single channel monolithically integrated photoreceiver consumes a power of  $6\text{ mW}$  and demonstrates an optical bandwidth of  $0.8\text{ GHz}$ . Eight-channel photoreceiver arrays are designed for massively parallel applications where low power dissipation and low crosstalk are required. The array is on a  $250\text{-}\mu\text{m}$  pitch and can be easily scaled to much higher density. Large signal operation up to  $1\text{ Gb/s}$  is achieved with crosstalk less than  $-26\text{ dB}$ . A scheme for time-to-space division multiplexing is proposed and demonstrated with the photoreceiver array.

**Index Terms**—Photoreceiver, SiGe HBT, transimpedance amplifier.

## I. INTRODUCTION

OPTOELECTRONIC integrated circuits offer the advantages of both optics—massive interconnectivity and parallelism, and microelectronics—high gain and decision making capability. From a technological point of view, Si-based optoelectronic devices are of great interest for densely-packed free-space interconnects and time division multiplexing (TDM) systems. Cost, reliability, and compatibility with CMOS technology are the key factors. Besides low cost and high reliability, Si technology provides very-large-scale-integration complexity where dense arrays of receivers, modulators and switching circuits can be fabricated on a single chip.

Compared to CMOS transistors, heterojunction bipolar transistors (HBTs) have several advantages which make their use more preferable in high-speed optoelectronic integrated circuits. These advantages include lower noise figure at high bit rate, better power-added efficiency and higher  $f_T$  at lower bias voltages [1]. Recent advances in the growth of SiGe/Si heterostructures have led to high-performance Si-based HBTs [1]–[5]. The incorporation of strained SiGe as the base layer in Si-based transistor technology greatly enhances the frequency

response of the transistor. Cutoff frequency and maximum oscillation frequency exceeding  $90\text{ GHz}$  and  $110\text{ GHz}$ , respectively, have recently been achieved with this heterostructure [4], [5]. There have also been efforts to realize optoelectronic devices, such as detectors, photoreceivers and light emitters with Si-based heterostructures [6]–[15]. With these components integrated on a single chip, many smart functions such as routing and switching can be performed at high speed. We have recently reported the characteristics of a  $0.5\text{-GHz}$  single channel SiGe/Si monolithically integrated p-i-n/HBT photoreceiver circuit [15]. A  $1\text{ Gb/s}$  low-power CMOS photoreceiver has also been recently reported [12]. In this paper we demonstrate, for the first time, eight-channel monolithically integrated photoreceiver arrays made with SiGe/Si HBTs. The array exhibits a uniform  $-3\text{ dB}$  bandwidth of  $0.8\text{ GHz}$ , adjacent channel crosstalk of less than  $-26\text{ dB}$ , and dissipates  $6\text{ mW}$  per channel. Operating with  $2\text{-V}$  bias, the array can be interfaced directly with CMOS circuits. The optoelectronic integrated circuit (OEIC) design, heterostructure growth and fabrication procedure are described in Section II. Device and circuit characteristics are described and discussed in Section III. The characteristics of multiple-channel photoreceiver arrays are described and analyzed in Section IV. Finally, the results are summarized in Section V.

## II. PHOTORECEIVER CIRCUIT FABRICATION

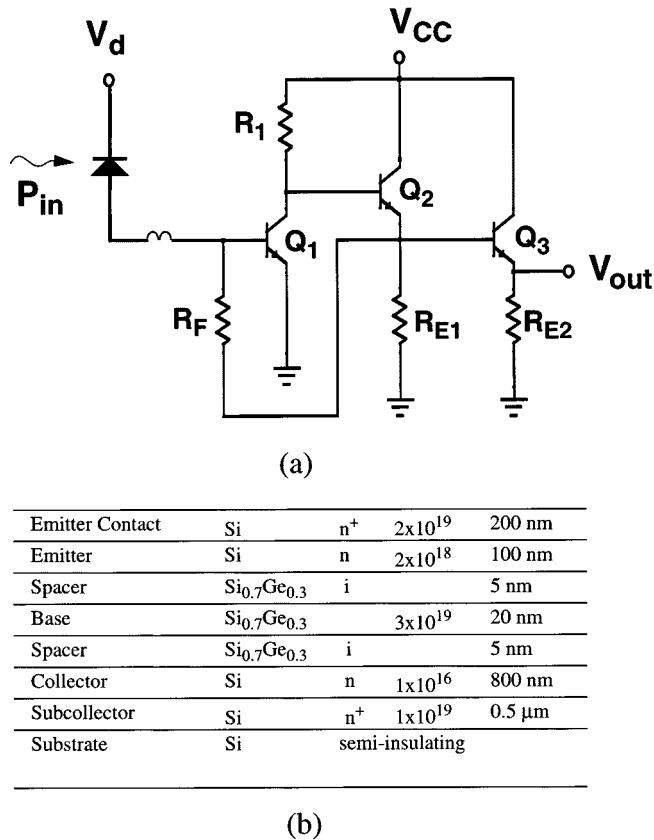

Fig. 1(a) shows the circuit diagram of a single channel of the photoreceiver array. It consists of a  $p^+$ -n-n<sup>+</sup> photodiode and a three-stage transimpedance amplifier with a  $550\text{-}\Omega$  feedback resistor and  $50\text{-}\Omega$  matching output stage. The first stage consists of the feedback amplifier which is designed to stabilize the operating points and increase the bandwidth of the circuit. The output stage consists of a two-stage emitter follower which is used to maximize the dynamic range of the amplifier. The three-stage amplifier is realized with N-p-N double heterojunction SiGe/Si HBTs. The feedback resistor ( $R_F$ ), biasing resistors, and bias voltage ( $V_{cc}$ ) are designed to optimize the circuit performance; mainly the bandwidth, circuit gain and noise characteristics. An inductor is inserted at the input of the circuit to enhance the photoreceiver bandwidth and improve the signal-to-noise ratio of the amplifier. It is important to note that both the photodiode and HBT can be realized by one step epitaxy. The base/collector/subcollector layers of the HBT also serve as the  $p^+$ /n/n<sup>+</sup> layers of the photodiode. This integration scheme has been used with great success by us [16] and others [17], [18] to realize  $1.55\text{ }\mu\text{m}$  high-speed single- and multichannel photoreceivers.

Manuscript received March 29, 2000; revised June 30, 2000. This work was supported by the Army Research Office (MURI program) under Grant DAAG 55-98-1-0288.

O. Qasaimeh, Z. Ma, and P. Bhattacharya are with the Solid-State Electronics Laboratory, Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109-2122 USA.

E. T. Croke is with HRL Laboratories, LLC, Malibu, CA 90265 USA.

Publisher Item Identifier S 0733-8724(00)09823-6.

Fig. 1. (a) Equivalent circuit of single channel transimpedance amplifier photoreceiver. (b) SiGe/Si heterojunction bipolar transistor grown by molecular beam epitaxy.

The schematic of the SiGe/Si heterostructure, grown by molecular beam epitaxy (MBE), on high-resistivity (001) Si substrate, is shown in Fig. 1(b). A uniform Ge composition profile of 30% is used for the base layer which is doped p-type with boron. This results in a large band offset ( $\Delta E_v$ ) at the base-emitter (BE) junction and provides larger current gain. Moreover, a large Ge content at the BE junction enhances the wet etch selectivity and reduces the risk of over-etching the base layer. Spreading resistance analysis (SRA) shows that the base doping concentration is larger than  $3 \times 10^{19} \text{ cm}^{-3}$ . The thickness of the base layer (300 Å) is made less than the  $\text{Si}_{0.7}\text{Ge}_{0.3}/\text{Si}$  critical thickness to prevent the formation of dislocations. The outdiffusion of boron, which may occur during growth, results in junction displacement toward the emitter, away from the SiGe/Si heterojunction. Such displacement would introduce parasitic homojunction effects and results in a reduction in the current gain and the cutoff frequency of the HBT. To eliminate outdiffusion of boron from the base layer, unintentionally doped 50 Å  $\text{Si}_{0.7}\text{Ge}_{0.3}$  spacer layers were inserted on both sides of the base layer.

The circuit fabrication procedure is as follows: first the emitter metal (Cr/Au=500/2000 Å) is selectively formed on the highly doped emitter contact layer by evaporation and liftoff techniques. The emitter mesa is then formed by a selective potassium hydroxide (KOH)- based wet etch. This etching introduces an undercut that allows the selective placement of a self-aligned base contact. The emitter metal is then alloyed

by rapid thermal annealing (RTA) for 20 s at 400 °C. After evaporating the base metal (Pt/Au=200/1300 Å), the base mesa is formed by reactive ion etching (RIE). The collector contact (Ti/Au=500/2000 Å) is then evaporated and annealed for 7 s at 375°C. The devices is then isolated using RIE and passivated with a 1  $\mu$ m thick SiO<sub>2</sub> layer. Via holes in the SiO<sub>2</sub> layer are opened by RIE, and interconnection metal (Ti/Al/Ti/Au=500/11 000/500/2000 Å) and airbridges are finally deposited.

The emitter layer is etched to obtain the  $p^+-n-n^+$  photodiode wherein the collector region is used as the absorption layer. The base layer is used as the p-contact while the subcollector as the n-contact. The heterostructure was designed with a thick  $0.8\ \mu m$  collector/absorber layer in order to reduce electron diffusion and thereby improve the bandwidth of the photodiode. To enhance the responsivity of the photodiode, the thickness of the  $SiO_2$  passivation layer was designed to minimize light reflection at  $0.85\ \mu m$ .

The resistors were fabricated by electron beam evaporation of NiCr ( $700 \pm 10$  Å). The film thickness controls the resistor value. The measured sheet resistance of the film is  $25 \Omega/\square$ . The spiral inductor was fabricated using the interconnection metallization and air-bridge technology to form the central terminal. The nominal value of the spiral inductor is  $\sim 2.5 \pm 0.5$  nH.

### III. DEVICE AND CIRCUIT PERFORMANCE

### A. HBT Characteristics

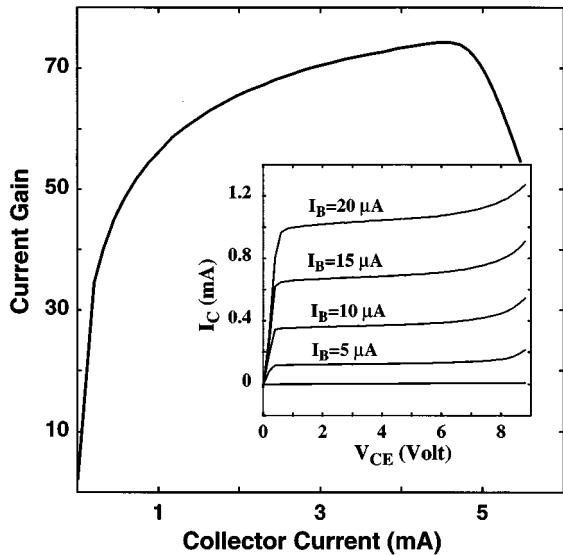

The dc and RF characteristics of the fabricated HBTs were measured. The dc current gain of a typical device is shown in Fig. 2. The common-emitter current–voltage characteristics are shown in the inset. As can be seen in the figure, the devices operate with a reasonably high current gain at low collector current ( $\beta > 30$  at  $I_c = 200 \mu\text{A}$ ). It is also evident that the devices have a reasonably high breakdown voltage ( $> 10\text{V}$ ). The offset voltage is very close to zero, indicating symmetric and base-emitter (BE) and base collector (BC) junctions. From the Gummel plots, the collector and base ideality factors are calculated to be  $n_c = 1.16$  and  $n_b = 2.35$ , respectively. The latter value indicates that the base current is dominated by recombination in the space-charge regions. The  $S$ -parameters of the devices were measured using a HP8510 network analyzer and coplanar microwave probes, and from these measurements the cutoff frequency ( $f_T$ ) and maximum oscillation frequency ( $f_{\max}$ ) of the device are calculated to be 18 GHz and 27 GHz, respectively. It should be noted that the 3 dB bandwidth of the present circuit is really limited by the frequency response of the photodiode [15]. Higher values of  $f_T$  and  $f_{\max}$  have been realized by us with similar HBTs designed for MMICs [19]. The measured dc and RF characteristics were used to extract the small- and large-signal models of the HBTs, which were, in turn, used to optimize the characteristics of the photoreceiver circuit. The values of the biasing and feedback resistors and the bias voltage of the photoreceiver circuit were then evaluated.

### B. Transimpedance Amplifier

Three-stage transimpedance amplifiers, without the p<sup>+</sup>-n-n<sup>+</sup> photodiodes, were designed, and fabricated using SiGe/Si HBTs

Fig. 2. Measured dc common-emitter current gain as a function of collector current. The inset shows typical current-voltage characteristics of the HBT.

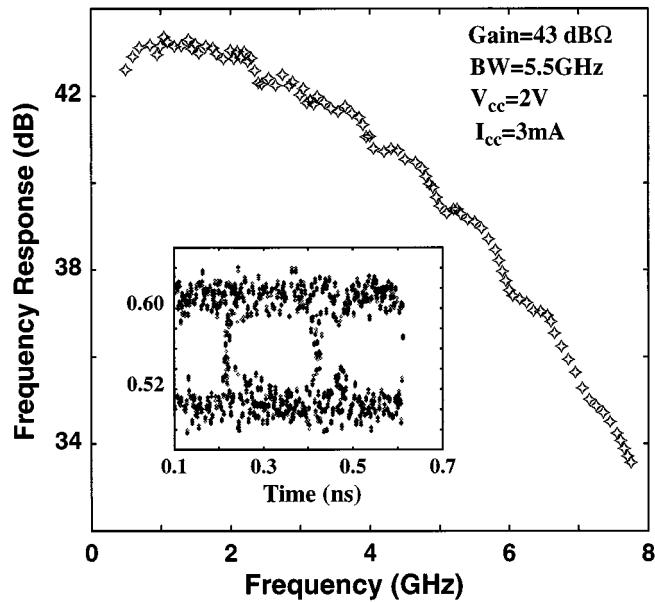

with an emitter size of  $5 \mu\text{m} \times 5 \mu\text{m}$ . The amplifier *S*-parameters were measured in the frequency range of 0.1 to 10 GHz and the effective electrical transimpedance gain,  $Z_{\text{eff}} = 50 |S_{21}| / |1 - S_{11}|$ , was derived. The fabricated amplifiers have a  $-3 \text{ dB}$  bandwidth of 5.5 GHz and a gain of  $43.5 \text{ dB}\Omega$  at  $V_{CC} = 2 \text{ V}$ , as shown in Fig. 3. This corresponds to a transimpedance gain-bandwidth product of 0.825 THz. The eye diagram of the circuit, measured at a bit rate of 5 Gbit/s with a  $2^{31}-1$  word long nonreturn-to-zero (NRZ) pseudorandom bit stream, is shown in the inset of Fig. 3. A clear eye opening with minimum inter-symbol interference and jitter is observed. The percentage jitter and eye closure, obtained from the figure, are 22.5% and 41%, respectively. One of the more important issues in densely packed arrays is the total power dissipation. Therefore, the single amplifier should provide higher gain at lower current and bias values. The total power dissipation of the fabricated amplifier is 6 mW at  $V_{CC} = 2 \text{ V}$ . We believe that an even lower value of the power dissipation can be obtained if the circuit is optimized with respect to  $R_C$  and  $R_E$ .

### C. Photoreceiver Circuit

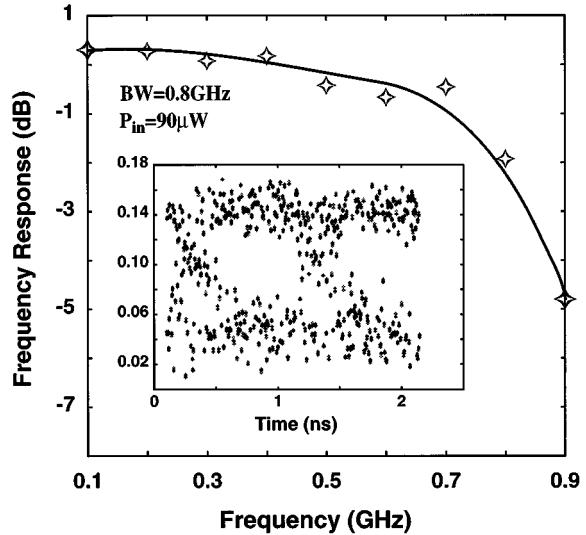

Monolithically integrated photoreceivers consisting of the three-stage transimpedance amplifier, inductor, and a  $p^+-n-n^+$  photodiode were designed and fabricated. The photodiode has a  $12 \mu\text{m} \times 13 \mu\text{m}$  lateral dimension and a ring-shaped *p*-type contact. Antireflection coating, suitable for operation with  $0.85 \mu\text{m}$  light, was incorporated on the top surface by plasma enhanced deposition of  $\text{SiO}_2$ . The fabricated *p-n* photodiode, with AR coating, exhibits a breakdown voltage as high as  $-20 \text{ V}$  and leakage current less than 150 nA at  $-2 \text{ V}$ . The responsivity of the photodiode is measured to be  $\sim 0.3 \text{ A/W}$  at 880 nm. The bandwidth of the photoreceiver was measured using a high-speed single-mode edge-emitting GaAs laser ( $\lambda = 880 \text{ nm}$ ) and HP8593A spectrum analyzer. The laser was modulated with a HP8350 sweeper oscillator and coupled onto a single mode fiber. The modulated light was focused onto

Fig. 3. Measured frequency response of the transimpedance amplifier at  $V_{CC} = 2 \text{ V}$ . The inset shows the measured eye diagram at 5 Gb/s.

Fig. 4. Measured frequency response of a single channel p-i-n/HBT photoreceiver. The inset shows the measured eye diagram of the photoreceiver at 1 Gb/s.

the photodiode with a tapered optical probe and the electrical response of photoreceiver was measured by the spectrum analyzer. The highest measured bandwidth of the photoreceiver, which is limited by the bandwidth of the photodiode, was 0.8 GHz at 2 V applied bias. The frequency response is shown in Fig. 4. This relatively low bandwidth is attributed to the slow diffusion mechanism in the subcollector region. The total photocurrent of a *p-n* photodiode consists of fast (drift) and slow (diffusion) components, which arise from the carrier generation in the depletion region and subcollector region of the photodiode structure, respectively. The estimated RC time constant of the photodiode is  $\sim 32 \text{ ps}$  which corresponds to  $f_{RC}$  of  $\sim 31 \text{ GHz}$ . The measured eye diagram of the photoreceiver at a bit rate of 1 Gb/s is shown in the inset of Fig. 5. The

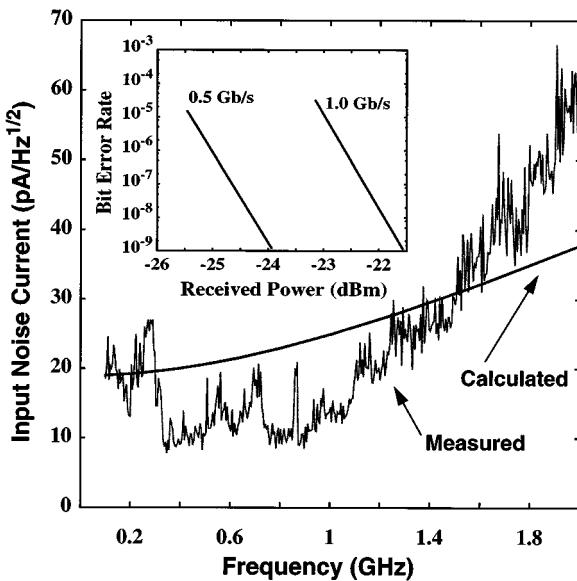

Fig. 5. Measured and calculated photoreceiver equivalent input noise. The inset shows the calculated bit error rates at 0.5 Gb/s and 1 Gb/s.

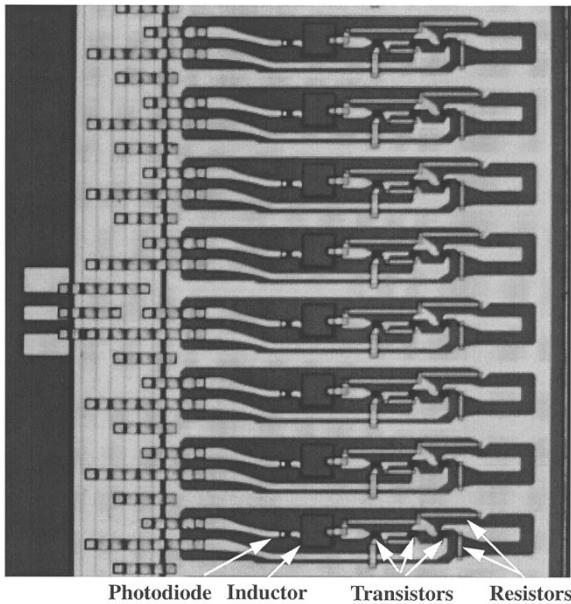

Fig. 6. Photomicrograph of the monolithically integrated eight-channel SiGe/Si p-i-n/HBT photoreceiver array.

diagram shows a clear eye opening with percentage jitter and eye closure of 45% and 54%, respectively.

Since we could not measure the photoreceiver sensitivity directly, the equivalent noise current at the input was calculated by summing all the noise sources. Thermal noise, generated from the biasing resistors and shot noise, generated from base and collector currents of the HBTs, were considered in the calculation. The calculation was carried out with the help of HSPICE, using typical operating conditions of the HBTs, the photodiode and the feedback and bias resistors. The output noise voltage of the photoreceiver was measured with a spectrum analyzer. The equivalent input noise current of the photoreceiver was calcu-

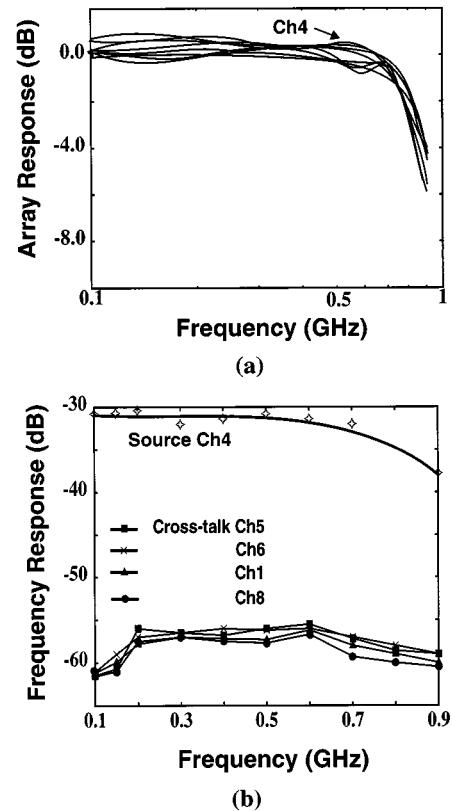

Fig. 7. (a) Measured individual channel frequency response of the eight-channel array; (b) measured frequency response of channel 4 and adjacent channel crosstalk in the eight-channel array.

lated from the output noise voltage and the RF characteristics of the circuit. The measured and calculated data are shown in Fig. 5. The photoreceiver sensitivity, shown in Fig. 5, is estimated to be  $-23.9$  dBm at 0.5 Gb/s for bit error rate of  $10^{-9}$ .

#### IV. MULTICHANNEL PHOTORECEIVER ARRAYS

Multichannel ( $8 \times 1$ ) photoreceiver arrays were designed and fabricated in a similar manner, as described in the previous section. Fig. 6 shows the photomicrograph of the array, which is the largest in size realized to date with SiGe/Si technology. The array size is  $1.5 \times 2$  mm with interchannel spacing of  $250 \mu\text{m}$ . Good uniformity in the frequency response between individual photoreceiver elements is achieved, as shown in Fig. 7(a). The eight channels show near-identical frequency response with a  $-3$  dB bandwidth of  $0.7 \pm 0.1$  GHz and an average transimpedance gain of  $44 \pm 2$  dB $\Omega$ . The yield of the discrete devices is more than 95%, which results in about 50% yield for the fabricated arrays. The crosstalk was measured by photoexciting channel 4 and measuring the RF output at the adjacent channels. The measured crosstalk is shown in Fig. 7(b). Special care was taken to ensure that there is no feedforward to the output in the absence of the input optical signal. The maximum crosstalk, measured within the 0.8 GHz bandwidth of the photoreceiver, is less than  $-26$  dB. The crosstalk can be further reduced by incorporating shielding that covers most of the photoreceiver circuit, as has been demonstrated by us with InP-based  $1.55 \mu\text{m}$  photoreceiver arrays [16].

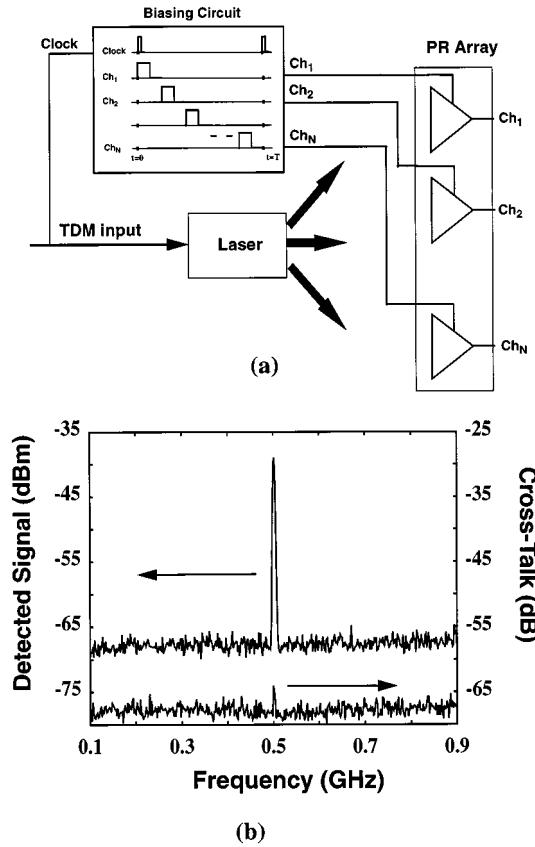

Fig. 8. (a) An optical-to-electrical space division multiplexing scheme using a multichannel photoreceiver array; (b) measured individual channel response and adjacent channel crosstalk in such a scheme.

The overall crosstalk is a combination of optical and electrical crosstalk. The optical crosstalk was eliminated by the experimental arrangement. As the data in Fig. 7(b) indicate, the crosstalk signal from channel 5 is only  $\sim 1$  dB higher than from channel 8. Electrical crosstalk is a result of microwave power propagating through the interconnection lines and the parasitic capacitors, and therefore the circuit layout may be important. It is worth noting that the crosstalk measured in our arrays does not show a peaking around the  $-3$  dB bandwidth frequency, as is usually the case in InP-based  $1.55\text{ }\mu\text{m}$  photoreceivers [16]. In the latter, the peaking frequency ( $f_{\text{peak}}$ ) is mainly due to the LC time constant associated with the spiral inductor and the equivalent input capacitance of the circuits. In the present circuit, the  $-3$  dB bandwidth (which is limited by the optical bandwidth of the photodiode) is much lower than  $f_{\text{peak}}$ .

An optical-to-electrical space division multiplexing system can be realized with the photoreceiver array. The concept is illustrated in Fig. 8(a). A time division multiplexed (TDM) signal is superimposed on the laser drive circuitry and the output optical TDM signal is distributed, by fiber or holographic means to the  $N$ -channel photoreceiver array. The TDM electrical signal is also used to sequentially trigger  $N$  channels of photoreceiver biasing ( $V_{cc}$ ) signals. Each channel of the array is biased with pulses having a period  $T$  and duty cycle  $T_d$ . For incoming  $N$  light signals, each signal can be routed through a specific photoreceiver channel in a short time,  $T_d$ , which is determined by the photoreceiver bandwidth. It should

be noted that power dissipation in the photoreceiver array is significantly reduced in this system. To test such a scheme, only one channel (4) was pulsed biased. An optical signal from a GaAs laser ( $\lambda = 0.88\text{ }\mu\text{m}$ ) modulated at  $f_m = 0.5\text{ GHz}$ , is coupled into channel 4 and the photoreceiver output is monitored by a spectrum analyzer. The signal  $f_m$  was detected for various values of  $T$  and  $T_d$  with minimum noise and crosstalk. The detected signal and crosstalk are shown in Fig. 8(b). In this scheme, the choice of  $T$  and  $T_d$  would depend on  $N$  and  $f_m$ , where  $N$  is the number of photoreceiver channels.

## V. CONCLUSION

Monolithically integrated eight-channel photoreceiver arrays realized with SiGe/Si technology were designed, fabricated and characterized. The array demonstrates state-of-the-art performance characteristics, which are suitable for massively parallel applications. Low power dissipation of  $6\text{-mW}/\text{channel}$  and low adjacent channel crosstalk of  $-26\text{ dB}$  were measured. The array also demonstrates a uniform  $-3\text{ dB}$  bandwidth of  $0.8\text{ GHz}$  at  $2\text{ V}$  applied bias in each channel.

## REFERENCES

- [1] S. Subbanna, G. Freeman, D. Ahlgren, D. Greenberg, D. Harame, J. Dunn, D. Herman, and B. Meyerson, "Integration and design issues in combining very-large-speed silicon-germanium bipolar transistors and ULSI CMOS for system-on-a-chip applications," in *IEDM Tech. Dig.*, Washington, DC, Dec. 1999, pp. 845–847.

- [2] A. Schüppen, A. Gruhle, H. Kibbel, U. Erben, and U. König, "SiGe-HBT's with high  $f_T$  at moderate current densities," *Electron. Lett.*, vol. 30, pp. 1187–1188, 1994.

- [3] G. Freeman, D. Ahlgren, D. Greenberg, R. Groves, F. Huang, G. Hugo, B. Jagannathan, S. Jeng, J. Johnson, K. Schonenberg, K. Stein, R. Volant, and S. Subbanna, "0.18  $\mu\text{m}$  90 GHz  $f_T$  SiGe HBT BiCMOS, ASIC-compatible, copper interconnect technology for RF and microwave applications," in *IEDM Tech. Dig.*, Washington, DC, Dec. 1999, pp. 569–572.

- [4] A. Schüppen, U. Erben, A. Gruhle, H. Kibbel, H. Schumacher, and U. König, "Enhanced SiGe heterojunction bipolar transistors with 160 GHz- $f_{\text{max}}$ ," in *IEDM Tech. Dig.*, Washington, DC, Dec. 1995, pp. 743–746.

- [5] K. Oda, E. Ohue, M. Tanabe, H. Shimamoto, T. Onai, and K. Washio, "130 GHz- $f_T$  SiGe HBT Technology," in *IEDM Tech. Dig.*, Washington, DC, Dec. 1997, pp. 791–794.

- [6] R. A. Soref, "Silicon-based optoelectronics," *Proc. IEEE*, vol. 81, pp. 1687–1706, Dec. 1993.

- [7] S. Fujita, T. Suzuki, A. Matsuoka, S. Miyazaki, T. Torikai, T. Nakata, and M. Shikada, "High sensitivity 5 Gbit/s optical receiver module using Si IC and GaInAs APD," *Electron. Lett.*, vol. 26, pp. 175–176, 1990.

- [8] H. Hamano, T. Yamamoto, Y. Nishizawa, Y. Oikawa, H. Kuwatsuka, A. Tahara, K. Suzuki, and A. Nishimura, "10 Gbit/s optical front end using Si-bipolar preamplifier IC, flipchip APD, and slant-end fiber," *Electron. Lett.*, vol. 27, pp. 1602–1605, 1991.

- [9] Y. S. He, L. D. Garrett, K.-H. Lee, and J. C. Campbell, "Monolithically integrated silicon nMOS pin photoreceiver," *Electron. Lett.*, vol. 30, pp. 1887–1888, 1994.

- [10] M. Yamamoto, M. Kubo, and K. Nakao, "Si-OEIC with a built-in pin-photodiode," *IEEE Trans. Electron. Devices*, vol. 42, pp. 58–63, 1995.

- [11] M. Kyomasu, "Development of an integrated high speed silicon PIN photodiode sensor," *IEEE Trans. Electron. Devices*, vol. 42, pp. 1093–1099, 1995.

- [12] C. L. Schow, J. D. Schaub, R. Li, J. Qi, and J. C. Campbell, "A monolithically integrated 1-Gb/s silicon photoreceiver," *IEEE Photon. Tech. Lett.*, vol. 11, pp. 120–121, 1999.

- [13] Y. S. Tang, W.-X. Ni, C. M. Sotomayor Torres, and G. V. Hansson, "Fabrication and characterization of Si-Si<sub>0.7</sub>Ge<sub>0.3</sub> quantum dot light emitting diodes," *Electron. Lett.*, vol. 31, pp. 1385–1386, 1995.

- [14] O. Qasaikeh, P. Bhattacharya, and E. Croke, "SiGe-Si quantum-well electroabsorption modulators," *IEEE Photon. Tech. Lett.*, vol. 10, pp. 807–809, 1998.

- [15] J. Rieh, D. Klotzkin, O. Qasaimeh, L. Lu, K. Yang, L. P. Katehi, P. Bhattacharya, and E. Croke, "Monolithically integrated SiGe-Si PIN-HBT front-end photoreceivers," *IEEE Photon. Tech. Lett.*, vol. 10, pp. 415-417, 1998.

- [16] A. L. Gutierrez-Aitken, P. Bhattacharya, K.-C. Syao, K. Yang, G. I. Haddad, and X. Zhang, "Low crosstalk (< -40 dB) in 1.55 mm high-speed OEIC photoreceiver arrays with novel on-chip shielding," *Electron. Lett.*, vol. 32, pp. 1706-1708, 1996.

- [17] E. Sano, M. Yoneyama, S. Yamahata, and Y. Matsuoka, "23 GHz bandwidth monolithic photoreceiver compatible with InP/InGaAs double heterojunction bipolar transistor fabrication process," *Electron. Lett.*, vol. 30, pp. 2064-2065, 1994.

- [18] L. Lunardi, S. Chandrasekhar, C. Burrus, R. Hamm, J. Sulhoff, and J. Zyskind, "A 12-Gb/s high-performance, high-sensitivity monolithic p-i-n/HBT photoreceiver module for long-wavelength transmission systems," *IEEE Photon. Technol. Lett.*, vol. 7, pp. 182-184, 1995.

- [19] J. Rieh, L. Lu, L. P. B. Katehi, P. Bhattacharya, E. Croke, G. Ponchak, and S. Alterovitz, "X- and Ku-Band amplifiers based on Si/SiGe HBT's and micromachined lumped components," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 685-694, 1998.

**Omar Qasaimeh** received the B.S. and M.S. degrees in electronic engineering from Jordan University of Science and Technology, Irbid, Jordan, in 1992 and 1994, respectively. He is currently pursing the Ph.D. degree at the University of Michigan, Ann Arbor.

His research interests include the fabrication, modeling, and characterization of high-speed SiGe and III-V optoelectronic integrated devices and circuits.

**Zhenqiang Ma** (S'98) received the B.S. degree in applied physics and the B.E. degree in electrical engineering from Tsinghua University, Beijing, China, in 1991. He received the M.S. degree in materials and the M.S.E. degree in electrical engineering from the University of Michigan, Ann Arbor, in 1997, where he is currently pursuing the Ph.D. degree in electrical engineering.

His research interests include novel aluminum metallization for integrated circuits and flat panel displays, SiGe-based semiconductor materials, physics, microwave device technologies, device long-term reliability and the application of SiGe HBT in high-speed and high-power MMIC.

**Pallab Bhattacharya** (M'78-SM'83-F'89) received the Ph.D. degree from the University of Sheffield, U.K., in 1978.

He is the James R. Mellor Professor of Engineering and Professor of Electrical Engineering and Computer Science at the University of Michigan, Ann Arbor. His teaching and research interests include molecular beam epitaxy of elemental and III-V compound semiconductors, materials characterization, electronic and optoelectronic devices, and optoelectronic integrated circuits. From 1978 to 1983, he was on the faculty of Oregon State University, Corvallis, and since then he has been with the University of Michigan. He was an Invited Professor at the Ecole Polytechnic Federale de Lausanne, Switzerland, from 1981 to 1982. He has published over 300 technical articles in archival journals. He is the author of the textbook *Semiconductor Optoelectronic Devices* (Englewood Cliffs, NJ: Prentice-Hall, 1994, 1st ed., and 1997, 2nd ed.).

Dr. Bhattacharya is an Editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES and has edited *Properties of Lattice-Matched and Strained InGaAs* (U.K.: INSPEC, 1993) and *Properties of III-V Quantum Wells and Superlattices* (U.K.:INSPEC, 1996). He has served on the Advisory Board of the Electrical and Communications Systems Division at the National Science Foundation. He has also served on several other committees and panels in government, industry, and technical conferences. He has received the Parker Rhodes Scholarship from the University of Sheffield, the Research Excellence Award from the University of Michigan, the Alexander von Humboldt Award, the John Simon Guggenheim Award, IEEE (LEOS) Distinguished Lecturer Award, the SPIE Technology Achievement Award, the Paul Rappaport Award and the S.S. Attwood Award from the University of Michigan. He is a Fellow of the Optical Society of America and a member of the American Physical Society and Sigma Xi.

**Edward T. Croke** received the B.S. degree from Cornell University, Ithaca, NY, in 1986, and the Ph.D. degree from the California Institute of Technology, Pasadena, in 1991.

He joined Hughes Research Laboratories, Malibu, CA, in April of 1991, where he has primarily been involved with the growth of Si-related heterostructures including SiGe and SiGeC alloys by MBE. He is currently responsible for the research direction, design of experiments, and program marketing efforts on behalf of Raytheon Co. and Hughes Electronics Corp. through HRL Laboratories, LLC. During his employment with HRL, he designed and implemented a novel carbon source for e-beam deposition of SiGeC random alloys. He demonstrated coherent growth of SiGeC/Si superlattices on (100) Si substrates by MBE and discovered a dramatic improvement in the surface morphology and crystallinity of high-Ge and high-C content SiGeC/Si superlattices through the use of Sb as a surfactant. He has also developed growth methods for suppressing Sb segregation, enhancing dopant profile abruptness, and increasing mechanical stability in highly metastable SiGe/Si heterostructures. He has authored or coauthored more than 30 journal articles relating to the subject of MBE growth of Group IV heterostructure electronic materials.