# A Ka Band Extended Resonance Power Amplifier

Adam L. Martin and Amir Mortazawi, *Member, IEEE*

**Abstract**—A Ka-band power amplifier based on an extended resonance power combining technique is presented. This technique enables the design of planar microstrip power amplifiers that are much more compact than those based on traditional quarter-wave hybrid designs. The extended resonance power combining amplifier presented here combines four GaAs MESFET's at 32.8 GHz using a planar structure that is more than 40% smaller than a quarter-wave hybrid power combining amplifier design, while the power-combining efficiency is 92%. The measured small-signal gain at 32.8 GHz is 4.6 dB, and at 1-dB compression the output power is 23.3 dBm with a power-added efficiency of 12.8%.

**Index Terms**—Extended resonance, Ka band, power combining.

## I. INTRODUCTION

THE millimeter-wave frequency range is now host to a number of consumer wireless communication networks, such as LMDS, VSAT, and digital radio. Affordable implementation of these systems requires a cost-effective MMIC solution to generating sufficient transmit power at these frequencies. Since power-combining of multiple transistors is usually necessary, one must carefully consider the optimal circuit design in terms of maintaining a high power-combining efficiency, keeping the overall size to a minimum, and providing isolated paths for the dc and RF to eliminate bias tees. Planar power combining techniques usually employ quarter-wave hybrids to combine power from several individual amplifiers (e.g., corporate combiners, series combiners, etc.). The available output power is often dictated by the loss associated with these hybrids, and this is particularly true for millimeter-wave applications [1]–[4]. Obviously, circuit losses can be diminished if the overall circuit size is reduced.

Presented here is a millimeter-wave power combining amplifier based on an alternative planar circuit design that requires neither quarter-wave hybrids, nor separate  $50\ \Omega$  matching networks for each transistor and results in a much smaller structure. An extended resonance technique is used to space transistors the proper distance from each other to form a resonant power dividing/combining structure with which quarter-wavelength spacing between transistors can be avoided. Instead, the spacing is such that the input/output admittance of one transistor is converted to its conjugate value at the input/output of the next transistor, similar in concept to coupled cavity waveguide filters.

Manuscript received May 11, 2000; revised September 25, 2000. This work was supported by a grant from Lockheed-Martin Corporation.

A. L. Martin is with M/A-COM, Roanoke, VA 24061 USA (e-mail: amm@eos.ncsu.edu).

A. Mortazawi is with the Electrical and Computer Engineering Department, North Carolina State University, Raleigh, NC 27695 USA.

Publisher Item Identifier S 1051-8207(00)10942-0.

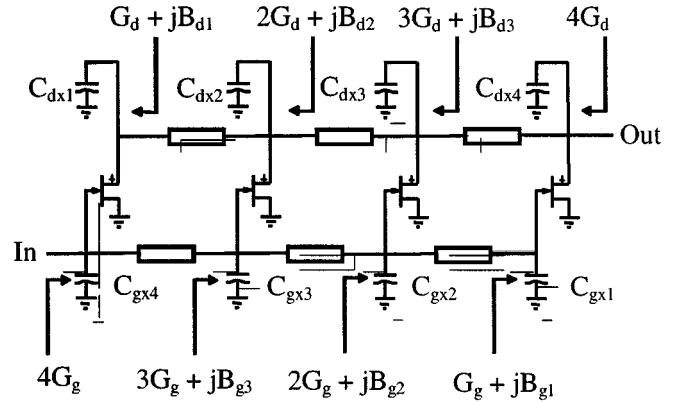

Fig. 1. Generic power combining amplifier based on the extended resonance technique.

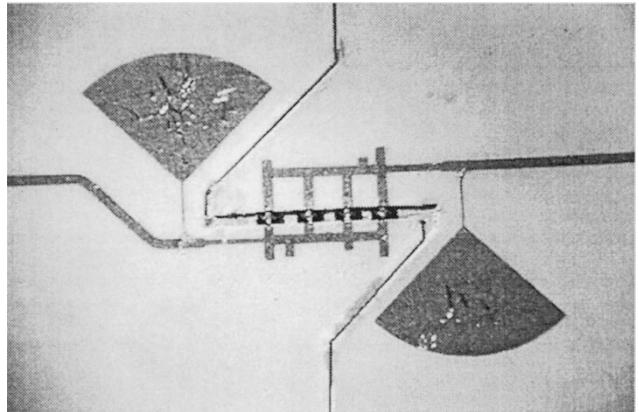

Fig. 2. Photograph of a four-device extended resonance power amplifier at 33 GHz.

## II. THEORY

The power combiner in Fig. 1 is a generic example of combining four FET's with extended resonance dividing/combining networks. Each network incorporates either the gate or drain admittance of each FET into a series of filter-like sections that are each designed so that the resulting voltage magnitude at the edge of each transmission line section is equal [5]. The equivalent input circuit for each FET is a shunt conductance,  $G_g$ , and capacitance,  $C_g$ , while the FET equivalent output circuit is a shunt  $G_d$ , and  $C_d$ . External shunt capacitors/inductors are included in both circuits to match the phase delay along each section in both circuits. The first section of the input circuit is designed by transforming the complex admittance at the first FET,  $G_g + jB_{g1}$  [where  $B_{g1} = 2\pi f(C_g + C_{gx1})$ ], to its conjugate,  $G_g - jB_{g1}$ , at the gate of the second FET. The second filter section is designed by transforming the complex admittance at the second

FET,  $2G_g + j(B_{g2} - jB_{g1})$  [where  $B_{g2} = 2\pi f(C_g + C_{gx2})$ ], to its conjugate,  $2G_g - j(B_{g2} - jB_{g1})$ , at the gate of the third FET, and so on. Ultimately, the input admittance to the power dividing section is  $3G_g + j(B_{g3} - jB_{g2} + B_{g1})$  [where  $B_{gi} = 2\pi f(C_g + C_{gxi})$  for  $i = 1$  to 3], which can be matched to  $50 \Omega$  with a single-stub matching network. The output circuit design proceeds in a similar way, however, in the reverse direction, beginning at the drain of the fourth FET and progressing in the direction of the drain of the first FET.

### III. DESIGN

A four-device power-combining amplifier at 32.8 GHz has been designed and constructed based on the extended resonance approach discussed above, a photograph of the amplifier is shown in Fig. 2. All external shunt capacitors are realized with open-circuited microstrip stubs. The active devices are Alpha 0.25  $\mu\text{m}$  GaAs MESFET chips AF035p1-00 each biased at 5 V with a drain current of 70 mA. The devices are mounted to the ground plane with conductive silver epoxy and the gates and drains are wire bonded to the microstrip lines. The microstrip circuit is constructed on a 0.127 mm thick Rogers TMM3 substrate ( $\epsilon_r = 3$ ).

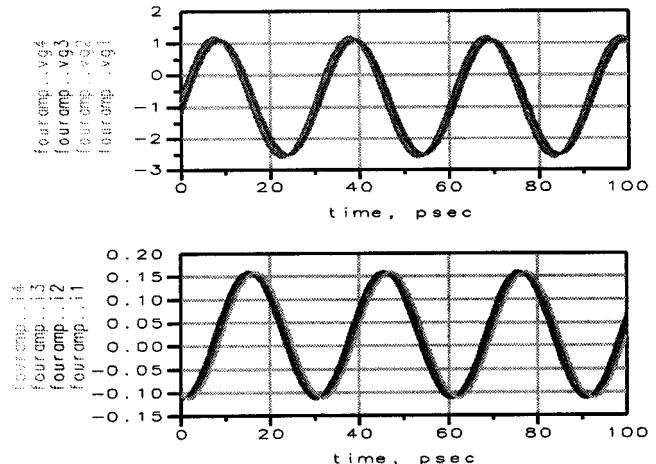

The simulated gate voltage and drain current waveforms for each device in the extended resonance amplifier are shown in Fig. 3. As can be seen the gate voltages and the drain currents are equal to each other confirming the power dividing/combining characteristics of this circuit.

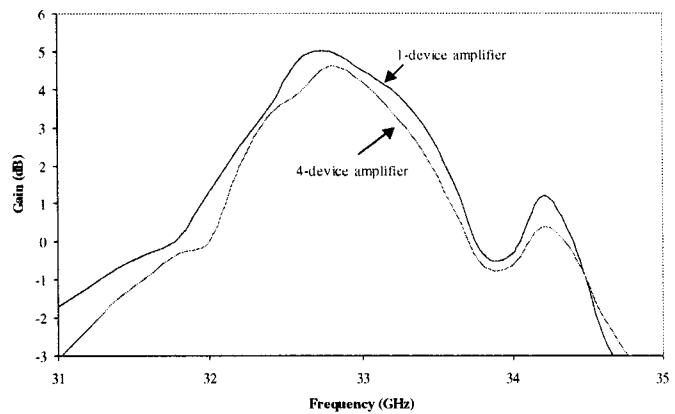

The measured small-signal gain for the four-device amplifier as well as for a single-device amplifier is illustrated in Fig. 4. At 32.8 GHz, the gain of the extended resonance amplifier and single-device amplifier are 4.6 dB and 5.0 dB, respectively (the single device amplifier was designed using single stub matching at the input and output). This agrees well with the predicted gain of 6.0 dB at 33 GHz for each amplifier based on HP ADS<sup>TM</sup> simulations. The accuracy between predicted and measured results would be improved by developing better models for the wire bonds connecting the chips to microstrip lines. The 1-dB and 3 dB bandwidth of the extended resonance amplifier are approximately 0.8 GHz and 1.2 GHz respectively, neither of which are significantly compromised compared to the single-device amplifier, which exhibits a similar bandwidth.

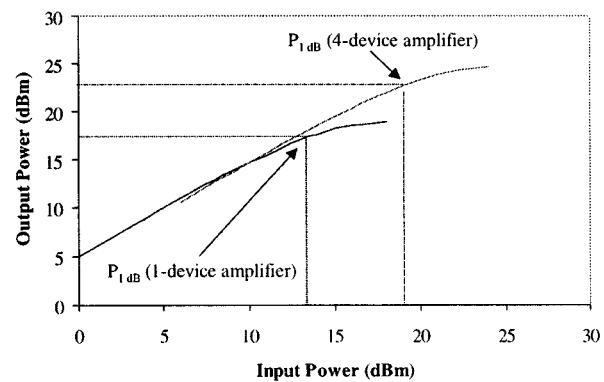

The large-signal performance of both the four-device extended resonance amplifier and the single-device amplifier have been observed by increasing the input power until ultimately both were driven into 3-dB compression (Fig. 5). The 1-dB compression point for the single-device amplifier corresponds to an input power of 17.6 dBm, while the same compression point for the extended resonance power amplifier corresponds to an input power of 23.3 dBm. A comparison of the saturated output from both amplifiers indicates a power-combining efficiency of approximately 93%. It should be mentioned that both amplifiers designed were based on the simultaneous conjugate match.

The power-added efficiency of the extended resonance power amplifier under 1-dB compression is 12.8%, while it increases to 15.1% under 3-dB compression.

Fig. 3. Simulated gate voltage and drain current for each device in the extended resonance power amplifier.

Fig. 4. Measured small-signal gain for single-device and four-device extended resonance power amplifier.

Fig. 5. Gain compression curves for the single-device and four-device power amplifiers.

### IV. CONCLUSIONS

A Ka-band power amplifier prototype has been presented based on a new power-combining technique that has demonstrated excellent power-combining efficiency while yielding a very compact structure. This type of structure is also capable of meeting the bandwidth requirements of many mm-wave consumer-based communications systems. An MMIC version

of this amplifier is currently in the design process, which will include an input driver as well as larger devices in the output stage in order to demonstrate a fully functional power amplifier that can be integrated into these systems.

#### ACKNOWLEDGMENT

The authors would like to thank L. Mirth and J. Hubert of Lockheed Martin, Orlando FL, for useful discussions and information provided during this project.

#### REFERENCES

- [1] K. Chang and C. Sun, "Millimeter-wave power combining techniques," *IEEE Microwave Theory Tech.*, vol. MTT-31, pp. 91–107, Feb. 1983.

- [2] J. Gipprich, L. Dickens, R. Hayes, and M. Restivo, "A compact LTCC multilayer multiport stripline coupler network for low-loss power combining/splitting," in *IEEE 3rd Topical Meeting on Electrical Performance of Electronic Packaging*, 1994, pp. 167–169.

- [3] G. Ferrell, L. Dickens, J. Gipprich, B. Hayes, and F. Sacks, "A high efficiency 10-Watt HBT power amplifier assembly using combining techniques," in *IEEE MTT Symp. Dig.*, vol. 2, 1995, pp. 327–330.

- [4] I. D. Robertson, Ed., *MMIC Design*, ser. IEE Circuits and Systems Series 7, 1995.

- [5] A. Martin, B. C. DeLoach, and A. Mortazawi, "An eight-device extended resonance power combining amplifier," *IEEE Microwave Theory Tech.*, vol. 48, pp. 844–850, June 1998.