# A PEEC with a New Capacitance Model for Circuit Simulation of Interconnects and Packaging Structures

Yi Cao, Zheng-Fan Li, Ji-Feng Mao, and Jun-Fa Mao, *Senior Member, IEEE*

**Abstract**—In this paper, a modified partial-element equivalent-circuit (PEEC) model, i.e.,  $(L_p, \vec{A}, R, \epsilon_f)$ PEEC, is introduced. In such a model, no equivalent circuit, but a set of state equations for the variables representing the function of circuit, are given to model a three-dimensional structure. Unlike the original  $(L_p, P, R, \epsilon_f)$ PEEC model, the definition of vector potential  $\vec{A}$  with integral form and the *Lorentz gauge* are used in expanding the basic integral equation instead of the definition of the scalar potential  $\varphi$  with integral form. This can directly lead to the state equations, and the capacitance extraction can be replaced by the calculation of the divergence of  $\vec{A}$ , which is analytical. For analysis of most interconnect and packaging problems, generally containing complex dielectric structures, the new model can save a large part of computing time. The validity of the new model is verified by the analysis in time and frequency domain with several examples of typical interconnect and packaging structures, and the results with this new method agree well with those of other papers.

**Index Terms**—Integrated circuit, interconnect and packaging, Lorentz gauge, PEEC, state equations.

## I. INTRODUCTION

THE operating frequency of high-speed integrated circuits (IC) has increased very fast in the past several years, and is approaching gigahertz range. Meanwhile, the system scale and integration density in modern IC's are also growing quickly with the appearance of some new packaging technologies such as the multichip module (MCM). As a result, in the design of a high-performance IC system, problems caused by interconnect and packaging structures such as dispersion, crosstalk, and packaging effects need to be properly solved. Therefore, simulation of the electromagnetic performance of these structures is required [1]–[8]. To model the interconnect and packaging structures, typically the geometric structure is subdivided into subsections that can be modeled by quasi-electrostatic and quasi-magnetostatic analysis tools, which ignore the coupling between the electric and magnetic fields, then extract the equivalent capacitance and inductance of these subsections to generate an equivalent circuit that can be dealt with by a circuit simulator. Thus, the electrical analysis of the geometric structures can be done in the same way of circuit simulation. These equivalent circuits can also be inserted into other kinds

of models of interconnect and packaging structures to perform a larger scale analysis. Since the interconnect and packaging structures in modern high-speed IC systems normally are complex three-dimensional (3-D) structures, except the long interconnection lines between the discontinuities, and the electric and magnetic characters exist simultaneously for these structures, the traditional quasi-static-based lumped-circuit simulating models, which contain only the single capacitance or single inductance, are no longer reasonable [2]. In this case, full-wave models such as the finite-difference time-domain (FDTD) method [3]–[5] and transmission-line matrix (TLM) method [6] can be used to model these structures. However, for large-scale IC systems that contain many components, it will be very time consuming to accurately model all of them by the full-wave methods. As another choice, an equivalent circuit or a network, consider the self and mutual effects are set up at first, then fit the parameter of every element from the results of the full-wave analysis [3], [4] or measurements [7]. In both of the above ways, extracting the network parameters to fit the equivalent circuit is still time consuming. As a compromise of the quasi-static and full-wave model, the partial-element equivalent-circuit (PEEC) [8]–[10] model can be a good choice for many interconnect and packaging problems. It can use much less computing time to give good accuracy due to extracting the parameter using quasi-static model, meanwhile considering both the electric and magnetic interactions. It is also convenient for PEEC to be inserted into other circuit models. To apply the PEEC model, partition the interconnect and packaging structures into inductive and capacitive cells, as in [9] at first, then calculate  $L$ 's and  $C$ 's of these partial elements from the quasi-static solution of Maxwell's equations. After that, connect these elements together to form a equivalent circuit, finally analyze the circuit consisting of these elements by a general circuit simulation tool, e.g., SPICE, to get the time-domain or frequency-domain solutions. In the original  $(L_p, P, R, \epsilon_f)$ PEEC model, the scalar potential is expanded in the integral form, thus the  $C$  matrix needs to be extracted. However, the calculation of  $C$ 's in complex dielectric structures is difficult, and it is also time consuming for a complicated system.

In this paper, a modified  $(L_p, \vec{A}, R, \epsilon_f)$ PEEC model is introduced. Starting from the integral expansion of vector potential  $\vec{A}$ , the Lorentz gauge and basic integral equation of the PEEC, a set of state equations can be obtained directly without using the integral expansion of the scalar potential  $\varphi$ . Thus, the extraction of capacitance parameters can be replaced by the calculation of

Manuscript received January 19, 1999. This work was supported by the National Natural Science Foundation of China.

The authors are with the Department of Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200030, China.

Publisher Item Identifier S 0018-9480(00)00844-9.

the divergence of the vector potential  $\vec{A}$  with an analytical form, and in this calculation, many data of  $L$ 's can be reused. In the new model, a set of state equations instead of an equivalent circuit are used to describe the geometric structure, which is suitable for the large-scale system reduction through the Padé approximation via Lanczos (PVL) process.

In Section II, the  $(L_p, \vec{A}, R, \varepsilon_f)$ PEEC model will be described in detail. In Section III, four circuits of different kinds are analyzed as examples by the new model to show that the  $(L_p, \vec{A}, R, \varepsilon_f)$ PEEC model agrees well with the  $(L_p, P, R, \varepsilon_f)$ PEEC model and it is accurate and efficient in analyzing the interconnect and packaging structures.

## II. THEORY

The PEEC model is based on the equation

$$-\frac{\partial}{\partial t} \vec{A}(\vec{r}, t) - \nabla \varphi(\vec{r}, t) = \vec{E}(\vec{r}, t) \quad (1)$$

where  $\vec{A}$  is the vector magnetic potentials and  $\varphi$  is the scalar electric potentials. Using the definition of  $\vec{A}$

$$\vec{A} = \frac{\mu}{4\pi} \int_{v'} \frac{\vec{J}(\vec{r}')}{|\vec{r} - \vec{r}'|} dv' \quad (2)$$

and discretize (1) through the Galerkin approach, for a  $K$  conductor system, it leads to the following equation:

$$R_{\gamma i} I_{\gamma i} + \sum_{k=1}^K \sum_{n=1}^{N_{\gamma k}} L_{pi, \gamma nk} \frac{d}{dt} [I_{\gamma nk}(t_{nk})] = \varphi_{+(i)} - \varphi_{-(i)} \quad (3)$$

where  $\gamma = x, y, z$ ,  $N_{\gamma k}$  is the total number of cells in the  $\gamma$  direction on conductor  $k$ ,  $+(i)$ , and  $-(i)$  are the index of the nodes or capacitive cells connected to inductive cell  $i$ . The way of cell partitioning is shown in [9, Figs. 1 and 2]. Equation (3) shows the volt–ampere relationship along an inductive cell. In the  $(L_p, P, R, \varepsilon_f)$ PEEC model,  $\varphi$  is next expanded by

$$\varphi = \frac{1}{4\pi\varepsilon} \int_{v'} \frac{\rho(\vec{r}')}{|\vec{r} - \vec{r}'|} dv' \quad (4)$$

then from (3), the discrete approximation of the electric-field integral equation with  $\vec{J}$  and  $q$  as unknowns can be obtained as follows [9]:

$$\begin{aligned} R_{\gamma i} I_{\gamma i} + \sum_{k=1}^K \sum_{n=1}^{N_{\gamma k}} L_{pi, \gamma nk} \frac{d}{dt} [I_{\gamma nk}(t_{nk})] \\ = \sum_{k=1}^K \sum_{m=1}^{M_k} Q_{mk}(t_{mk}) [pp_{mk}^{+(i)} - pp_{mk}^{-(i)}] \end{aligned}$$

where  $pp_j^i$ 's are so-called potential coefficients. Following the above equation, and with the discrete version of the conservation of charge equation, an equivalent circuit implementing the relationship in (3) can be resulted. Utilizing circuit simulators such as SPICE on that circuit can then do the time- or frequency-domain analysis.

For all the inductive cells, (3) can be rewritten as

$$[L] \frac{d}{dt} [\mathbf{I}] = [\mathbf{T}][\varphi] + [\mathbf{R}][\mathbf{I}] \quad (5)$$

in which  $L_{ij} = L_{pij}$  are the entries of partial inductance matrix of all the inductive cells.  $[\mathbf{I}] = [I_1, I_2, \dots, I_n]^T$  is the vector of inductive branch currents, while  $[\varphi]$  is the vector of node potentials.  $[\mathbf{T}]$  reflects the connective relationship between the nodes and currents.  $[\mathbf{R}] = \text{diag}(R_{\gamma i})$  gives the resistance of every branch. Left-multiplying both sides of (3) by  $[L]^{-1}$ , we can get

$$\frac{d}{dt} [\mathbf{I}] = [L]^{-1} [\mathbf{T}][\varphi] + [L]^{-1} [\mathbf{R}][\mathbf{I}]. \quad (6)$$

If we analyze the system through state equations, (6) are those for the unknowns of inductive branch currents. However, for the state equations for the node potentials, we do not use the integral form of the scalar potential and the conservation of the charge equation like in the original PEEC model. We know that in (2), (4), and the Lorentz gauge

$$\nabla \cdot \vec{A} = -\mu\varepsilon_0\varepsilon_r \frac{\partial \varphi}{\partial t} \quad (7)$$

which concern  $\vec{A}$  and  $\varphi$ , if and only if two of the three are given,  $\vec{A}$  and  $\varphi$  can be uniquely determined. This indicates that the state equations of  $\varphi$ 's can be obtained from the Lorentz gauge. In order to get these state equations, we start from Lorentz gauge (2) and (7). At first, an integral form solution of  $\nabla \cdot \vec{A}$  should be found. In the following derivation, the dielectric is equivalent to some currents in the free-space environment, that is to say the source of the electromagnetic field is the total current instead of the conductor current [11]. If we add and subtract  $\varepsilon_0(\partial \vec{E} / \partial t)$  in the Maxwell equation for  $\vec{H} \nabla \times \vec{H} = \vec{J}^C + \varepsilon_0(\varepsilon_r - 1) \partial \vec{E} / \partial t + \varepsilon_0 \partial \vec{E} / \partial t$ , we will have the formula of the total current

$$\vec{J} = \vec{J}^C + (\varepsilon_0\varepsilon_r - \varepsilon_0) \frac{\partial \vec{E}}{\partial t} \quad (8)$$

where  $\vec{J}^C$  is the conductor current, and the remainder of the equations is the equivalent polarization current due to the dielectric. From the Maxwell's equations and Lorentz gauge in free space, we can get the wave equation of  $\vec{A}$  as follows:

$$\nabla^2 \vec{A} - \mu\varepsilon_0 \frac{\partial^2 \vec{A}}{\partial t^2} = -\mu \vec{J}^C - \mu(\varepsilon_0\varepsilon_r - \varepsilon_0) \frac{\partial \vec{E}}{\partial t}. \quad (9)$$

Taking the divergence of two sides of (9), it leads to

$$\begin{aligned} \nabla^2 (\nabla \cdot \vec{A}) - \mu\varepsilon_0 \frac{\partial^2 (\nabla \cdot \vec{A})}{\partial t^2} \\ = -\nabla \cdot (\mu \vec{J}^C) - \nabla \cdot \mu(\varepsilon_0\varepsilon_r - \varepsilon_0) \frac{\partial \vec{E}}{\partial t}. \end{aligned} \quad (10)$$

Similar to (2), the solution of  $\nabla \cdot \vec{A}$  can then be written in an integral form as

$$\nabla \cdot \vec{A} = \frac{\mu}{4\pi} \int_{v'} \frac{\nabla \cdot \vec{J}}{|\vec{r} - \vec{r}'|} dv'. \quad (11)$$

Equation (11) should be expanded as in the approach of solving integral equations. This will make  $\nabla \cdot \vec{A}$  a linear function of

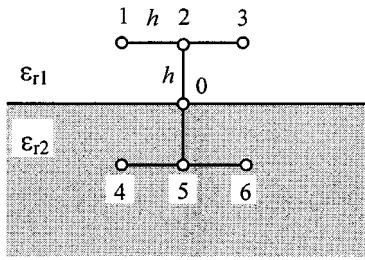

Fig. 1. Grid scheme for the discretization of  $\nabla \cdot \vec{A}$ .

$\nabla \cdot \vec{J}$ . In order to get the state equation for  $\varphi$ 's, i.e., a proper expression of  $\nabla \cdot \vec{A}$ ,  $\nabla \cdot \vec{J}$  is required to be a linear function of  $\vec{I}$ 's. From the Maxwell's equation  $\nabla \times \vec{H} = \epsilon(\partial \vec{E} / \partial t) + \vec{J}^C$ , and using the vector identity  $\nabla \times \nabla \times \vec{A} \equiv \nabla(\nabla \cdot \vec{A}) - \nabla^2 \vec{A}$ , we have

$$\frac{\partial \vec{E}}{\partial t} = \frac{1}{\mu \epsilon} \left[ \nabla(\nabla \cdot \vec{A}) - \nabla^2 \vec{A} \right] - \frac{\vec{J}^C}{\epsilon}. \quad (12)$$

Note that  $\nabla \cdot \epsilon(\partial \vec{E} / \partial t) = (\partial \rho / \partial t) = -\nabla \cdot \vec{J}^C$ , we then finally have the following expression of  $\nabla \cdot \vec{J}$ , which is a function of  $\vec{A}$ :

$$\begin{aligned} \nabla \cdot \vec{J} &= \nabla \cdot \vec{J}^C + \nabla \cdot (\epsilon - \epsilon_0) \frac{\partial \vec{E}}{\partial t} \\ &= \nabla \cdot \frac{\epsilon_0}{\mu \epsilon} \nabla^2 \vec{A} + \nabla \cdot \frac{\epsilon_0}{\epsilon} \vec{J}^C - \nabla \cdot \frac{\epsilon_0}{\mu \epsilon} \nabla(\nabla \cdot \vec{A}). \end{aligned} \quad (13)$$

The right-hand side of (13) can be divided into two parts: the divergence of conductor current  $\nabla \cdot \vec{J}^C$ , and the rest, the divergence of polarization current. Correspondingly,  $\nabla \cdot \vec{A}$  is also divided into two parts associate to the two parts of sources, respectively, and they will be calculated in different ways. The part of  $\nabla \cdot \vec{A}$  that originated by the polarization current can be calculated directly from (11). In order to do that, all the differential in (13) should be replaced by finite difference. Due to the identity  $\nabla \times \nabla \times \vec{A} \equiv \nabla(\nabla \cdot \vec{A}) - \nabla^2 \vec{A}$ , we can see that the divergence of polarization current  $\nabla \cdot (\epsilon_0 / \mu \epsilon) \nabla^2 \vec{A} - \nabla \cdot (\epsilon_0 / \mu \epsilon) \nabla(\nabla \cdot \vec{A})$  is zero in the uniform dielectric area. Thus, the integral in (11) only needed to be evaluated on the interface of two different media and the volume integral can be converted into a surface integral. As a two-dimensional (2-D) case example, following the grid scheme shown in Fig. 1,  $\int_{v'} [\nabla \cdot (\epsilon_0 / \mu \epsilon) \nabla^2 \vec{A} - \nabla \cdot (\epsilon_0 / \mu \epsilon) \nabla(\nabla \cdot \vec{A})] dv' / |\vec{r} - \vec{r}'|$  can be discretized as

$$\int_{S'} f(\vec{A}) dS' / |\vec{r} - \vec{r}'| \quad (14a)$$

and the value of  $f(\vec{A})$  is shown in (14b), at the bottom of this page, where  $K = (1/\epsilon_{r1}) - (1/\epsilon_{r2})$ , subscripts denote the number of nodes and components of vector potential. The integral area is along the interface of two different dielectric media.

According to (2),  $\vec{A}$  at a point of field domain can be approximately written as a linear combination of  $\vec{I}$ 's with coefficients that can be analytically calculated. Combined with (14),  $\nabla \cdot \vec{A}$  associate to the divergence of polarization current can finally be converted into a linear combination of  $\vec{I}$ 's.

To the conductor currents,  $\nabla \cdot \vec{A}$  associates to which part of the sources can be calculated in the following way. Integrate  $\nabla \cdot \vec{A} = \sum_{\gamma} (\partial A_{\gamma} / \partial \gamma)$  over the cell that shifted half the size from the inductive cell and with a node as its center (assuming the whole cell has the same potential, and for convenience, we also call these shift size cells the "capacitive" cells), on every direction we have

$$\int \int \frac{\partial A_{\gamma}}{\partial \gamma} d\gamma da_{\gamma} = (A_{\gamma+} - A_{\gamma-}) a_{\gamma} \quad (15)$$

where  $a_{\gamma}$  is the cross section,  $A_{\gamma+}$ ,  $A_{\gamma-}$  are the value of  $A_{\gamma}$  at two ends of the capacitive cell, or the two centers of the adjacent forward and backward inductive cells, and they can be the average value on this two cells as follows:

$$\bar{A}_{\gamma 2} = \sum_k \frac{\mu}{4\pi\epsilon_r} \int_{v_2} \int_{v_k} \frac{I_k}{a_k} \frac{1}{|\vec{r} - \vec{r}'|} dv_k dv_2 / l_{2\gamma} a_2 \quad (16)$$

Noticing the expansion of the *partial inductance* [12]  $L_{p21} = (\mu / 4\pi a_1 a_2) \int_{v_2} \int_{v_1} ((\vec{l}_1 \cdot \vec{l}_2) / |\vec{r} - \vec{r}'|) dv_1 dv_2$ , and that the vector potential has the same direction as the current, we have

$$\bar{A}_{\gamma 2} = \sum_k I_k L_{p2k} / l_{2\gamma} \epsilon_r. \quad (17)$$

For the simplicity of expression, all the inductive cells are assumed to have the same size, then the final expression can be obtained as follows:

$$\frac{\partial \varphi}{\partial t} = -\frac{l}{\mu \epsilon_0} \nabla \cdot \vec{A} = -\sum_{\gamma} \frac{1}{\mu \epsilon} \frac{\sum_i L_{p+,i} I_i - \sum_i L_{p-,i} I_i}{l_{\gamma}^2}. \quad (18)$$

We can see that in (18) when calculating the divergence of  $\vec{A}$ , most of the results of  $L_{p,ij}$  can be reused to save the computing time. We now have the complete expression of the divergence of the vector potential on every node. For all the nodes, the expression of  $\partial \varphi / \partial t$  can be written as

$$\frac{d}{dt} [\varphi] = [M][I] \quad (19)$$

which can be used as the state equations for the unknowns of node potentials. Combining (19) with (6), the state equations for all the unknowns are obtained as follows:

$$\frac{d}{dt} \begin{bmatrix} \varphi \\ I \end{bmatrix} = \begin{bmatrix} \mathbf{0} & \mathbf{M} \\ \mathbf{L}^{-1} \mathbf{T} & \mathbf{L}^{-1} \mathbf{R} \end{bmatrix} \begin{bmatrix} \varphi \\ I \end{bmatrix}. \quad (20)$$

$$f(\vec{A}) = \epsilon_0 \left[ K A_{2y} + K A_{5y} - K A_{0y} - \frac{1}{4} K A_{1y} - \frac{1}{4} K A_{3y} - \frac{1}{4} K A_{4y} - \frac{1}{4} K A_{6y} - \frac{1}{4} K A_{1x} + \frac{1}{4} K A_{3x} + \frac{1}{4} K A_{4x} - \frac{1}{4} K A_{6x} \right] / h^2 \quad (14b)$$

Since  $\varphi$  and  $\vec{J}$  have been discretized,  $\partial/\partial t$  has been replaced by  $d/dt$ . When the  $(L_p, P, R, \varepsilon_f)$ PEEC is used in the problems including complex dielectric media, the computation of potential coefficients  $pp_j^k$  is quite time consuming because the process contains many times of matrix inversion and multiplication. Compared with the original one, when the modified model is used, as described above, all the calculation needed for the divergence of  $\vec{A}$  is analytical and there is no matrix computation at all. These calculations are numerically equivalent to the extraction of capacitance parameters by the total charge Green's function method, and they use almost the same integral. Therefore, the accuracy of the modified model will not be decreased in comparison with the  $(L_p, P, R, \varepsilon_f)$ PEEC if they use the same partition form. In the derivation above, the retardation time in the propagation of the electromagnetic field is ignored for convenience. According to the typical size of the interconnect and packaging structure in modern IC systems this is reasonable. For a complete model, the retardation can be introduced similarly, as in the  $(L_p, \vec{A}, R, \varepsilon_f, \tau)$ PEEC model. The  $(L_p, \vec{A}, R, \varepsilon_f)$ PEEC model gives a set of state equations to describe the geometric structures instead of an equivalent circuit, which has an advantage in the hierarchical electromagnetic modeling of interconnect and packaging structure [8]. These equations can be easily combined with the equations describing other parts as a module to form a system that represents the whole structure. This system has the suitable form for large-scale system reduction through the PVL process.

### III. EXAMPLES AND RESULTS

In this section, several circuits and structures are analyzed as examples by the  $(L_p, \vec{A}, R, \varepsilon_f)$ PEEC model described in Section II. The structures in these examples are often encountered in IC interconnects and packages. For convenience, all the transmission lines are assumed to have zero thickness, but there is no difficulty to handle the conductors with finite thickness. The conductor currents are also assumed to be invariable along the cross section of the lines, except at the bend or discontinuity. In most of the interconnect and packaging structures in high-speed IC systems, this assumption is obviously correct. It also should be mentioned that, in order to compare our results with those from references, we use the first two example circuits with large size relative to a typical interconnect and packaging structure. Although in current frequency of the signal, the interconnection and packaging effects are still considerable for these structures.

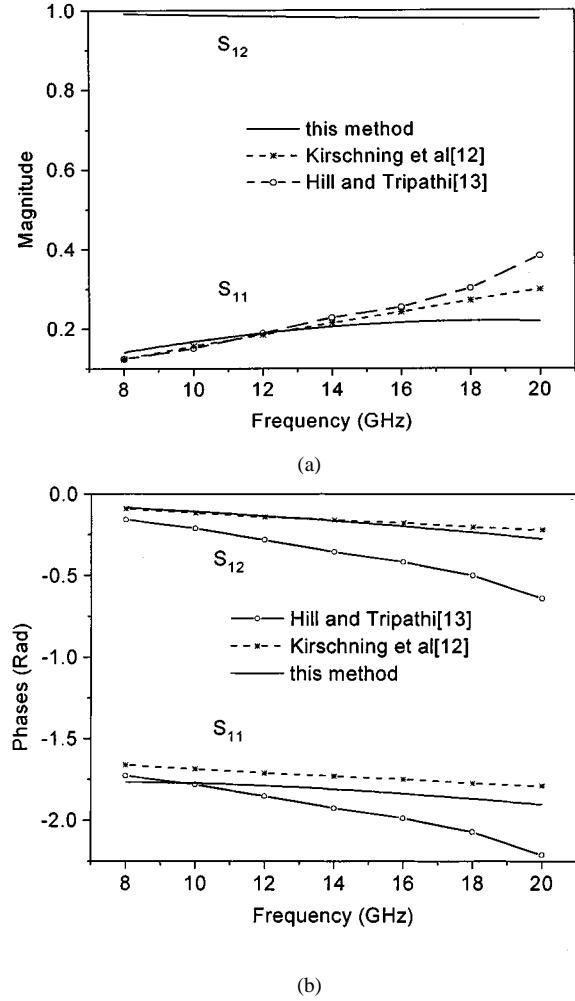

The first example is a right-angle bend in the microstrip line. The width of the microstrip is 0.635 mm, the height of the substrate is 0.635 mm, and the permittivity of the substrate is 9.8. The scattering parameters are calculated over the band of 8–20 GHz. The magnitude and phases of the scattering parameters from this method are shown in Fig. 2 compared with the results from [13] and [14]. The bend modeled here is in an open structure, as in [13], thus, the curves of  $S_{11}$  show some difference at higher frequencies.

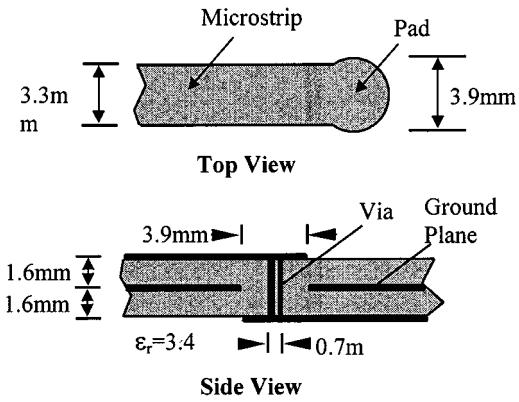

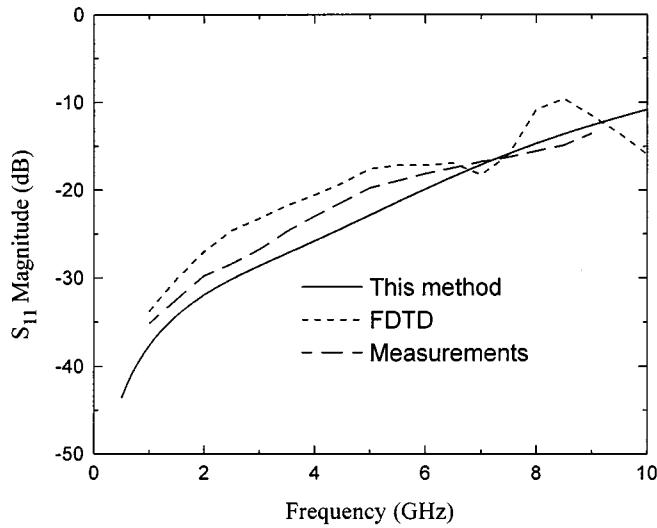

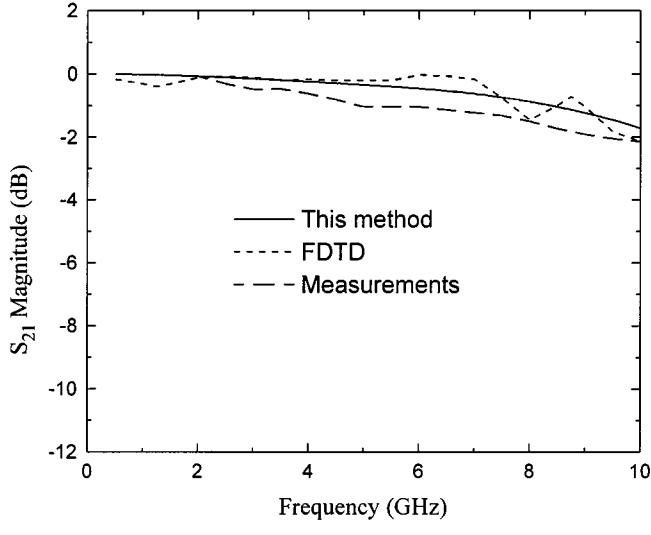

The second example is a cylindrical via the same as in [4], which is shown in Fig. 3. The via diameter is 0.7 mm, its length

Fig. 2.  $S$ -parameter of right-angle bend. (a) Magnitude of  $S_{11}$  and  $S_{12}$ . (b) Phase of  $S_{11}$  and  $S_{12}$ .

Fig. 3. The geometry of the cylindrical via.

is 3.2 mm, the pad diameter is 3.9 mm, and the width of the connecting microstrip is 3.3 mm. The dielectric slab has the thickness of 3.2 mm, and its permittivity is 3.4. There is a ground plane in the center of the slab, and it has a circular cutout with the diameter of 3.9 mm for the via. Part of the ground plane that is near the cutout is divided and modeled. The remainder is still regarded as an infinite large ground plane. Fig. 4 shows the comparison of  $|S_{11}|$  and  $|S_{21}|$  between this paper and [4].

(a)

(b)

Fig. 4 A comparison of: (a)  $|S_{11}|$  and (b)  $|S_{21}|$  from this method to the results in [4]

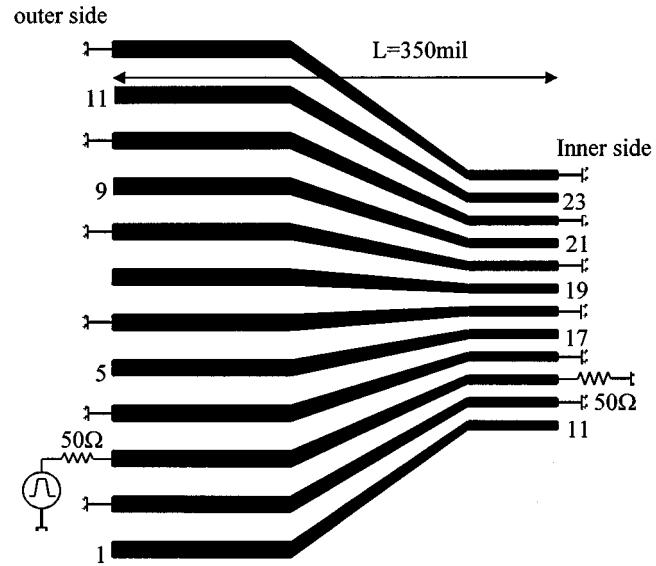

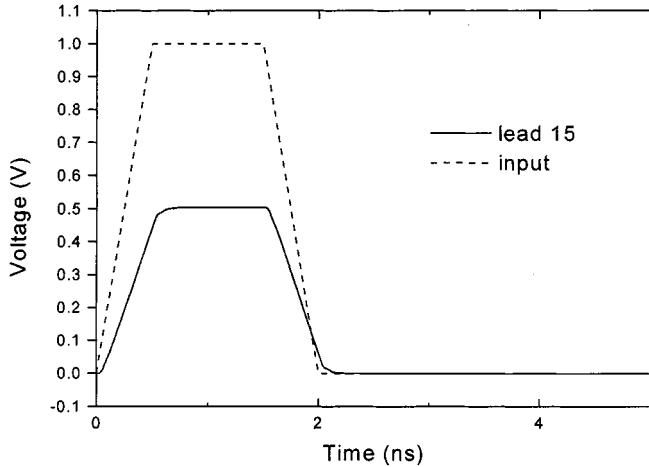

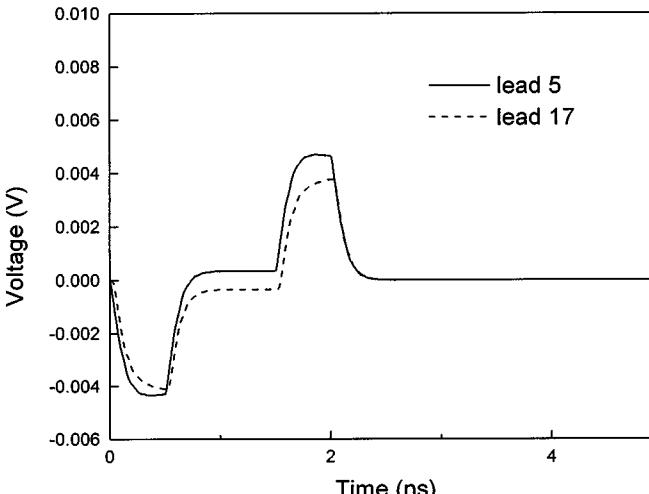

The third example analyzed is a 48-lead tape automated bonding (TAB) interconnect structure [7]. For simplicity, only the 12 leads at one side of the chip are considered. The geometry of it is shown in Fig. 5. We also assume that the coupling between the leads on different sides of the chip is negligible. At the inner side, lines have the width of 4 mil and the space between two adjacent lines is 8 mil. At the outer side, the values of the two parameter are 8 and 16 mil, respectively. The lines are embedded on a polyimide layer of 2-mil thick and with  $\epsilon_r = 3.6$ . In the analysis, we ground lead 2, 4, 6, 8, 10, and 12, and both ends of other leads are terminated by  $50\Omega$  resistance. Although the structure is relatively complex, the retardation time between cells is neglected because of the relatively small size. In the second example, for the same reason, the retardation time is also neglected. Lead 3 is excited by a trapezoidal pulse with the rise, roof, and fall times of 0.5, 1, and 0.5 ns, respectively. The waveform at lead 15 is shown in Fig. 6(a). Fig. 6(b) shows the waveform at leads 5 and 17.

Fig. 5. Geometry of the 12-lead TAB structure.

(a)

(b)

Fig. 6. Time-domain waveform at: (a) leads 15, (b) 5, and 17.

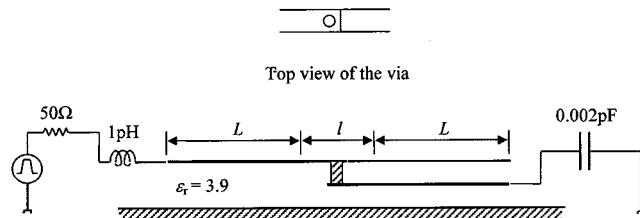

Fig. 7. Configuration of the fourth example circuit.

Fig. 8. Output waveform of example 4.

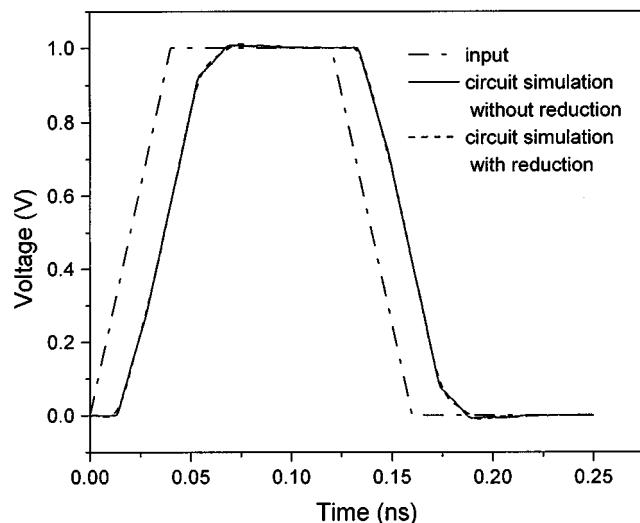

The last example will show the usage of the modified PEEC model in the hierarchical electromagnetic modeling. The geometry of the circuit is shown in Fig. 7, and is two transmission lines connected by a simple via. The width of the lines is 20  $\mu\text{m}$ ,  $l = 80 \mu\text{m}$ ,  $L = 1 \text{ mm}$ . The diameter of the via column is 16  $\mu\text{m}$ , the height of the column is 7  $\mu\text{m}$ , and the lower line is 7  $\mu\text{m}$  over the ground plane. The dielectric substrate has the permittivity of 3.9. The via is modeled by the modified PEEC model while the two transmission lines are modeled by the 2-D model. The whole system is reduced through the PVL process. Fig. 8 shows the output waveform through the structure. It can be seen that, because of the very small size, the effect of discontinuity is not considerable.

#### IV. CONCLUSION

A  $(L_p, \vec{A}, R, \epsilon_f)$ PEEC model is introduced in this paper. In this model, the integral-form definition of the vector magnetic and scalar electric potentials are replaced by the definition of the vector potential and Lorentz gauge in discretizing the basic integral equation of the PEEC model. To model a geometric structure that is partitioned into cells, a set of state equations for all the currents and node potentials on these cells are given instead of an equivalent circuit. Through this process, the computation of the capacitance parameter in the complex dielectric media structure, which is time consuming, is avoided. As the replacement, calculation of  $\nabla \cdot \vec{A}$  as a linear combination of  $\mathbf{I}$ 's

is needed, however, the coefficients in this combination can be analytically calculated. It should also be mentioned that when obtaining the discretized formulation of the Lorentz gauge, i.e., the state equations for potential unknowns, most of the partial inductance results can be reused to save the computing time. From various examples, it can be seen that the new model has the same flexibility and accuracy as the  $(L_p, P, R, \epsilon_f)$ PEEC model, and it is also very compatible to various system analysis tools.

#### REFERENCES

- [1] Y.-S. Tsuei, A. C. Cangellaris, and J. L. Prince, "Rigorous electromagnetic modeling of chip-to-package (first-level) interconnections," *IEEE Trans. Comp., Hybrids, Manufact. Technol.*, vol. 16, pp. 876–883, Dec. 1993.

- [2] K. Nabors, S. Kim, and J. White, "Fast capacitance extraction of general three-dimensional structures," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 1496–1506, July 1992.

- [3] P. Mezzanotte, M. Mongiardo, L. Roselli, R. Sorrentino, and W. Heinrich, "Analysis of packaged microwave integrated circuits by FDTD," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 1796–1801, Sept. 1994.

- [4] W. D. Becker, P. H. Harms, and R. Mittra, "Time-domain electronic analysis of interconnection in a computer chip package," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 2155–2163, Dec. 1992.

- [5] Y. Chen, P. Harms, R. Mittra, and W. T. Beyene, "An FDTD-Touchstone hybrid technique for equivalent circuit modeling of SOP electronic packages," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1911–1918, Oct. 1997.

- [6] M. Righi, G. Tardioli, L. Cascio, and W. J. R. Hoefer, "Time-domain characterization of packaging effects via segmentation technique," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1905–1910, Oct. 1997.

- [7] S. Sercu and L. Martens, "High-frequency circuit modeling of large pin count packages," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1897–1904, Oct. 1997.

- [8] W. Pinello, A. C. Cangellaris, and A. Ruehli, "Hybrid electromagnetic modeling of noise interactions in packaged electronics based on the partial-element equivalent circuit formulation," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1889–1896, Oct. 1997.

- [9] A. E. Ruehli, "Equivalent circuit models for three dimensional multiconductor systems," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-22, pp. 216–221, Mar. 1974.

- [10] H. Heeb and A. E. Ruehli, "Three-dimensional interconnect analysis using partial element equivalent circuits," *IEEE Trans. Circuits Syst. I*, vol. 39, pp. 974–982, Nov. 1992.

- [11] S. Ramo, J. R. Whinnery, and T. Van Duzer, *Fields and Waves in Communication Electronics*. New York: Wiley, 1965.

- [12] A. E. Ruehli, "Inductance computations in a complex integrated circuit environment," *IBM J. Res. Develop.*, vol. 16, pp. 470–481, Sept. 1972.

- [13] M. Kirschning *et al.*, "Measurements and computer aided modeling of microstrip discontinuities by an improved resonator method," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1983, pp. 495–497.

- [14] A. Hill and V. K. Tripathi, "An efficient algorithm for the three-dimensional analysis of passive microstrip components and discontinuities for microwave and millimeter-wave integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. 39, pp. 83–91, Jan. 1991.

**Yi Cao** received the B.S.E.E. degree in electronic engineering and the M.S. degree in electromagnetic field and microwave technology from Shanghai Jiao Tong University, Shanghai, China, in 1994 and 1996, respectively, and is currently working toward the Ph.D. degree at Shanghai Jiao Tong University.

His main areas of research are interconnects packages of high-speed IC's, including parameter extraction and circuit simulation and the numerical technique of solving field problems.

**Zheng-Fan Li** graduated from Tsinghua University, Beijing China, in 1958.

He was with Tsinghua University for 21 years—first as an Assistant, then a Lecturer, and finally as an Associate Professor. In 1979, he joined Jiao Tong University, Shanghai, China. He was with the Department of Electrical Engineering, Cornell University, Ithaca, NY, as a Visiting Scholar from 1981 to 1983. He is currently with the Department of Electronic Engineering, Jiao Tong University, as a Professor. He has performed research in the fields

of electromagnetic theory, radar system, microwave IC's, and microwave FET linear and nonlinear circuits. His current interests are in high-speed IC systems and packaging structures, including extraction of the circuit parameters and circuit simulation of IC systems under high-speed conditions. He is an editor for the *Journal of the China Institute of Communications* and the *Journal of Microwaves*.

Prof. Li is a committee member of the Microwave Communication Society of China.

**Ji-Feng Mao** received the B.S.E.E degree in electronic engineering from Shanghai Jiao Tong University, Shanghai, China, in 1996, and is currently working toward the M.S. degree at Shanghai Jiao Tong University.

His main area of research interest is electronic packaging of VLSI's, including placement and routing, extraction of circuit parameters, and analysis of signal integrity.

**Jun-Fa Mao** (M'92-SM'98) received the Ph.D. degree in electronic engineering from Shanghai Jiao Tong University, China, in 1992.

Since 1992, he has been a Faculty Member in the Department of Electronic Engineering, Shanghai Jiao Tong University, where he is currently a Professor and the Vice Dean. From 1994 to 1995, he was a Visiting Research Associate at the Chinese University of Hong Kong, Hong Kong. From 1995 to 1996, he was a Visiting Post-Doctoral Researcher with the ETHEICS Department, University of California at Berkeley. His research interests are computer-aided electrical analysis of high-speed interconnects (including superconducting interconnects) and packages of VLSI circuits.

Prof. Mao is a member of the New York Academy of Science.