# A New GaAs Variable-Gain Amplifier MMIC with a Wide-Dynamic-Range and Low-Voltage-Operation Linear Attenuation Circuit

Masahiko Inamori, Kaname Motoyoshi, Takahiro Kitazawa, Katsushi Tara, and Masahiro Hagio

**Abstract**—A 40-dB dynamic-range variable-gain amplifier (VGA) designed for the code division multiple access (CDMA) cellular phone has been developed. A wide-dynamic-range VGA under a low control voltage of 2.0 V, compatible with high linearity and low distortion characteristics, essential for CDMA, is realized by the new gain control technique. It greatly contributes to the high performance and small size of RF circuits for CDMA cellular handsets.

## I. INTRODUCTION

THE code division multiple access (CDMA) cellular phone system is expected to be the world standard because of the potential for high-capacity and high-quality communication. Output power control is essential for the CDMA cellular phone system because CDMA system has to solve the near-far problem. The demand for the higher performance variable-gain amplifier (VGA) has been growing as the CDMA cellular phone system is introduced worldwide.

VGA's for the CDMA system have been required wide dynamic range and high linear gain control as well as low-distortion characteristics over the variable output power level. In addition, low voltage operation is requisite to reduce the handset size. Several approaches of variable gain function such as VGA's and variable attenuators were reported with excellent characteristics by using GaAs MESFET's [1]–[6], but they could not simultaneously satisfy wide dynamic range, high linear gain control, low distortion, and low voltage operation.

This paper describes a VGA that controls the output power with wide dynamic range of 40 dB required for the RF part and low adjacent channel leakage power ratio (ACPR) of less than  $-53$  dBc sufficient for the CDMA system under low control voltage ( $V_c$ ) from 1.0 to 2.0 V. Such high performance suitable for CDMA is achieved by the new gain control technique ingeniously combining a couple of series FET's and a couple of shunt FET's to obtain linear gain control function.

## II. DESIGN OF VGA

### A. Configuration

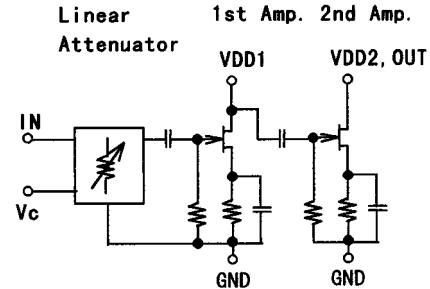

The circuit diagram of the newly developed VGA is shown in Fig. 1. The VGA consists of the linear attenuator and the

Fig. 1. Circuit diagram of the VGA.

two-stage amplifier. The linear attenuator positioned just before the two-stage amplifier controls the input signal from the upconverter by the externally applied control voltage  $V_c$ . The controlled power is amplified by the following constant gain two-stage amplifier and outputted from the drain of the final stage FET (VDD2). The linear attenuator is essential in the VGA for CDMA because it substantially determines the dynamic range, linearity of the gain control curve, and distortion characteristics.

### B. Linear Attenuator

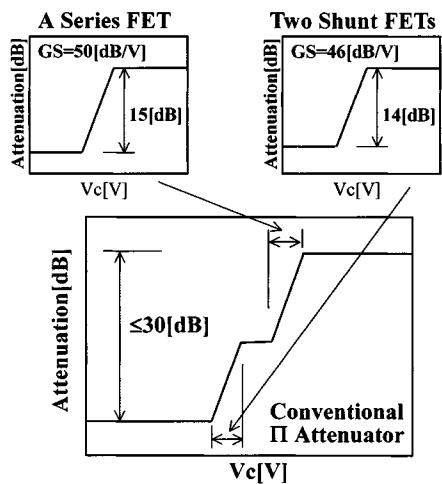

Conventional  $\Pi$  attenuator consists of one series FET and two shunt FET's, as shown in Fig. 2(a). Fig. 2(b) shows the example of a gain control curve of a series FET and that of two shunt FET's. Each dynamic range and gain slope (GS) are 15 dB and 50 dB/V for a series FET and 14 dB and 46 dB/V for two shunt FET's, respectively. The combination of these FET's results in less than 30-dB dynamic range, which is not enough for CDMA. Also, there is a kind of shoulder point in the gain control curve, which is a serious problem as a CDMA driver amplifier. Such nonlinearity is due to the discrepancy of the turn on/off point of the shunt FET and the turn off/on point of the series FET.

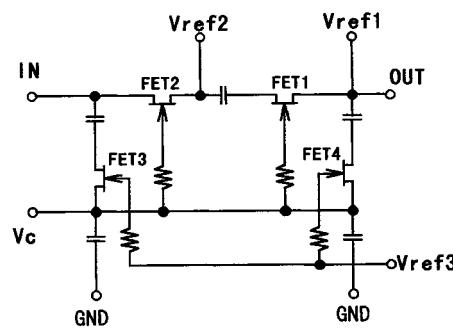

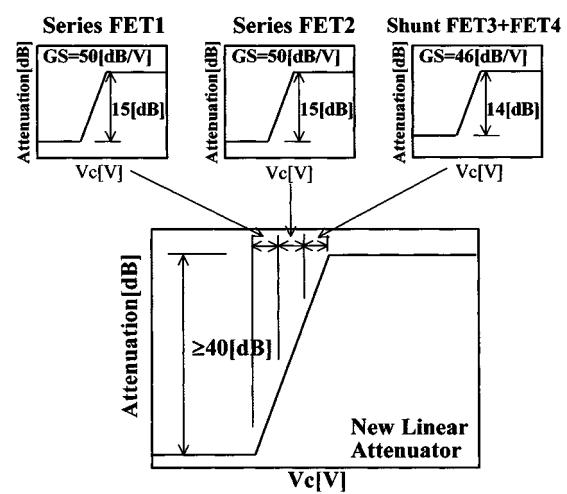

The new linear attenuator solves the problems of conventional  $\Pi$  attenuator and attains highly linear gain control and wide dynamic range. The new linear attenuator consists of cascaded dual-series FET's and shunt FET's, which has a kind of  $\Pi$  attenuator configuration, as shown in Fig. 3(a). Fig. 3(b) shows each gain control curve such as two shunt FET's of FET3,4, a series FET of FET1, and a series FET of FET2. To achieve the wide dynamic range of more than 40 dB, the new linear attenuator uses cascaded dual series FET's in the  $\Pi$  attenuator. Each series FET sequentially turns off/on to smoothly connect each gain control curve, resulting in high linearity gain control, as shown in Fig. 3(b). The dynamic range and GS of two shunt

Manuscript received October 28, 1999.

The authors are with the Discrete Device Division, Matsushita Electronics Corporation, Kyoto 617-8520, Japan.

Publisher Item Identifier S 0018-9480(00)00857-7.

(a)

(b)

Fig. 2. (a) Circuit diagram and (b) attenuation characteristics of the conventional II attenuator.

FET's, which is similar to that of a series FET, are 14 dB and 46 dB/V.

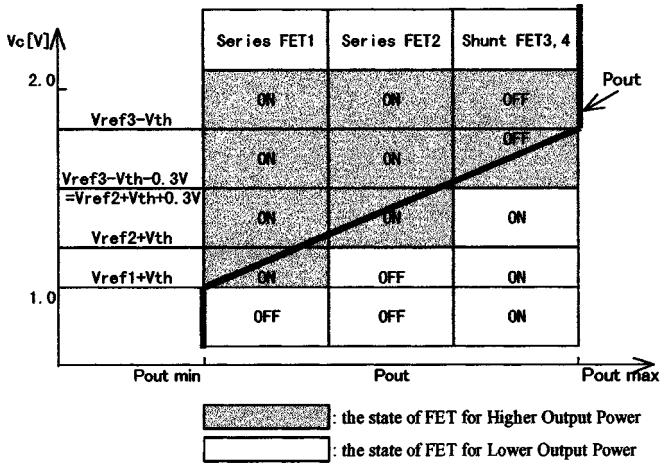

To connect each gain control curve smoothly, the  $V_c$  sequentially turn on/off the series FET's and shunt FET's referring to the bias voltages ( $V_{ref1}$ ,  $V_{ref2}$ , and  $V_{ref3}$ ), and each threshold voltage ( $V_{th}$ ) of FET's, noted as shown in Fig. 4. Each reference voltage is designed to overlap the gain control curve of each FET, obtaining a highly linear gain control curve, wide dynamic range, and low distortion at every point on the gain control curve.  $V_{ref1}$  and the  $V_{th}$  determine the complete turn-off point of FET1 in Fig. 3(a). In the region of  $V_c < V_{ref1} + V_{th}$ , FET1,2 are off state and FET3,4 are on state, resulting in the lowest output power. In the region of  $V_c < V_{ref1} + V_{th} < V_c < V_{ref2} + V_{th}$ , FET1 changes its on resistance depending on  $V_c$ , while FET2 is off state and FET3,4 are on state.  $V_{ref2}$  is assigned to smoothly connect the on-resistance variation curve of FET2 to the turn-on point of FET1. It is approximately 0.2 V higher than  $V_{ref1}$  because linearly varying region of FET's on resistance is less than 0.3 V. In the region of  $V_{ref2} + V_{th} < V_c < V_{ref2} + V_{th} + 0.3 V$  ( $= V_{ref3} - V_{th} - 0.3 V$ ), FET2 changes its on resistance while FET1,3,4 are on state. In the region of  $V_{ref2} + V_{th} + 0.3 V$  ( $= V_{ref3} - V_{th} - 0.3 V$ )  $< V_c < V_{ref3} - V_{th}$ , FET3,4 change its on-resistance toward complete off state, while FET1,2 are on state.

The shunt FET3, which is positioned between the input terminal and FET2, diverts the input signal in the region of

(a)

(b)

Fig. 3. (a) Circuit diagram and (b) attenuation characteristics of the new linear attenuator.

Fig. 4. Sequential operation of the new linear attenuator. The  $V_c$  sequentially turn on/off the series FET's and the shunt FET's referring to the  $V_{ref1}$ ,  $V_{ref2}$ ,  $V_{ref3}$ , and each  $V_{th}$  of FET's.

$V_c < V_{ref2} + V_{th} + 0.3 V$  ( $= V_{ref3} - V_{th} - 0.3 V$ ) in order to prevent the degradation of distortion characteristics in the low-gain condition.

In the present linear attenuator,  $V_{ref1}$  of 1.5 V,  $V_{ref2}$  of 1.7 V,  $V_{ref3}$  of 1.3 V, and each  $V_{th}$  of -0.5 V are designed to achieve wide dynamic range of 40 dB with high linearity under low control voltage of less than 2.0 V. Each reference voltage is provided

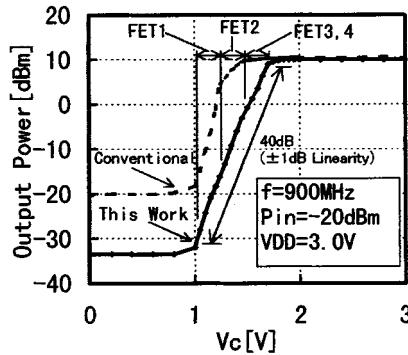

Fig. 5. Output power characteristics of the VGA as a function of control voltage. The new VGA shows wide dynamic range of 40 dB with  $\pm 1$  dB linearity.

by the resistor bias circuit in the VGA monolithic microwave integrated circuit (MMIC). As a result of these optimizing bias of series and shunt FET's, the newly developed linear attenuator has the wide linear dynamic range under the low control voltage.

### C. Two-Stage Amplifier

The VGA is positioned between an upconverter and power-amplifier module. The power gain of the two-stage amplifier is designed to be more than 26 dB in the gain diagram of the cellular phone system. The amplifier uses a self-biased FET for the stable operation. The gate length ( $L_g$ ) of the FET is designed as  $0.4 \mu\text{m}$  and  $V_{th}$  is  $-0.5$  V to achieve high power gain of more than 26 dB and low-circuit current of less than 30 mA. The gatewidths ( $W_g$ ) of the first-stage amplifier FET and the second-stage amplifier FET are determined to be 0.6 and 1.2 mm, respectively, in order to achieve output power of  $+6$  dBm with sufficiently low ACPR of less than  $-50$  dBc.

### III. FABRICATION

The MMIC is fabricated by the ion-implanted GaAs MESFET process with a lightly doped drain offset gate (LOG) self-aligned structure. The drain conductance ( $g_m$ ) and gate-drain breakdown voltage ( $BV_{gd}$ ) of the fabricated FET are 300 mS/mm and 18 V, respectively. The resistors are made of the highly ion-implanted region.

The  $\text{Ba}_{0.7}\text{Sr}_{0.3}\text{TiO}_3$  (BST) ferro-electric film, which has 50 times higher relative dielectric constant ( $\varepsilon_r$ ) than SiN film, is used for metal-insulator-metal (MIM) capacitors [2]. As a result, the chip size is so reduced that the VGA MMIC can be molded in the small-size six-pin plastic package of  $1.25 \text{ mm} \times 2.0 \text{ mm} \times 0.9 \text{ mm}$ .

### IV. RESULTS AND DISCUSSION

Fig. 5 shows the output power characteristics of the VGA as a function of  $V_c$ . The input power is  $-20$  dBm. The output power of the new VGA varies from  $-32$  to  $+8$  dBm with  $\pm 1$  dB linearity under  $V_c$  of  $1.0$  to  $2.0$  V. The gain control region is divided into three areas, and which FET dominates in each area is also shown in Fig. 5. It is shown that the wide dynamic range with

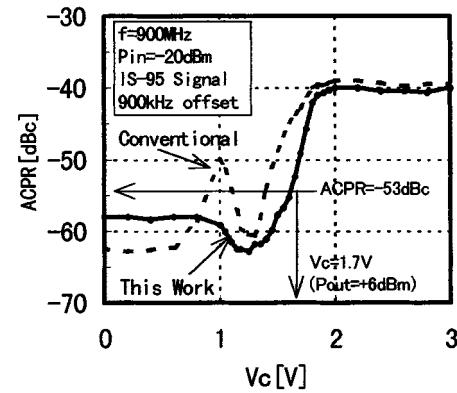

Fig. 6. ACPR characteristics of the VGA as a function of control voltage, measured at 900-kHz offset from the carrier. It should be noted that the new VGA indicates almost no distortion under the  $V_c$  region of 0 to 1.5 V.

Fig. 7. Equivalent-circuit models of (a) the conventional  $\Pi$  attenuator and (b) the new linear attenuator at  $V_c = 1.0$  V.

high linearity is obtained by smoothly connecting three areas. The characteristics of the VGA using conventional  $\Pi$  attenuator are also plotted in Fig. 5, which shows the linear dynamic range of less than 20 dB. Such narrow dynamic range is due to inappropriate overlapping of the gain control curve of a series FET and shunt FET's, and low drain-source isolation of a series FET.

The control voltage  $V_c$  for the new VGA, which is as low as  $1.0$ – $2.0$  V, corresponds to the output voltage of Si CMOS digital-to-analog (D/A) converters. Therefore, the new VGA can be controlled directly by the Si CMOS D/A converter, resulting in size reduction of the RF circuits in CDMA cellular handsets.

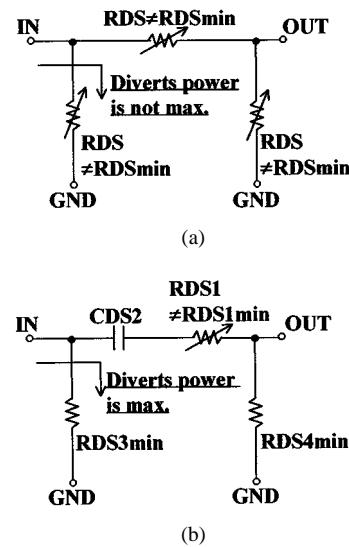

Fig. 6 shows the ACPR characteristics of 900-kHz offset from the carrier as a function of  $V_c$ . The new VGA shows the ACPR of less than  $-53$  dBc at an output power of  $+6$  dBm under the condition of  $V_c$  of  $1.7$  V, and low circuit current of  $28$  mA. Output power of  $+6$  dBm means that this VGA can directly drive the power-amplifier module for CDMA. On the other hand, the VGA using a conventional  $\Pi$  attenuator shows the degraded distortion characteristics in the low-power condition, as shown in Fig. 6, because the series FET turn-off/on and shunt FET's turn-on/off is not appropriately connected. Fig. 7(a) shows the

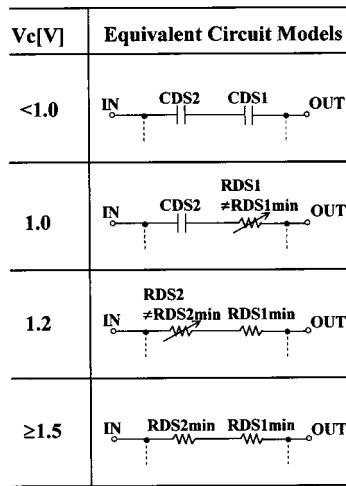

Fig. 8. Equivalent-circuit models of cascaded dual series FET's in the new linear attenuator. Each series FET is turned off/on at the different  $V_c$  bias point.

equivalent-circuit model of the conventional  $\Pi$  attenuator at  $V_c$  of 1.0 V. In the conventional  $\Pi$  attenuator, the shunt FET is not completely in the on state when the series FET is turned off at  $V_c$  of 1.0 V, as shown in Fig. 7(a). Therefore, the diverted input power that passes through the shunt FET's is limited by the high on resistance of the shunt FET's. Consequently it is unable to achieve sufficiently low ACPR characteristics for CDMA. Fig. 7(b) shows the equivalent-circuit model of the new linear attenuator at  $V_c$  of 1.0 V. In the new linear attenuator, the diverted input power, which passes through the shunt FET's, is higher than that of the conventional  $\Pi$  attenuator due to sequential operation of the series FET's and shunt FET's. Since these shunt FET's are completely on state when the series FET1 is turned off at  $V_c$  of 1.0 V, as shown in Fig. 7(b), it is consequently able to achieve sufficiently low ACPR characteristics for CDMA.

In addition, this gain control technique enables low-distortion characteristics at the higher input power conditions due to sequential operation of the series FET1 and series FET2. The distortion characteristics degrade at the control point of series FET turn off/on and shunt FET's turn on/off because of the nonlinearity of the GaAs MESFET. Fig. 8 shows the equivalent-circuit models of cascaded dual series FET's in the new linear attenuator. Each series FET is turned off/on at the different  $V_c$  bias point. In these bias conditions, it is able to prevent the overlap of distortion power between the series FET1 and series FET2. It should be noted that the new VGA indicates almost no distortion under the  $V_c$  region of 0 to 1.5 V and input power of -20 dBm, as shown in Fig. 6. This new VGA has high input power capability in CDMA systems.

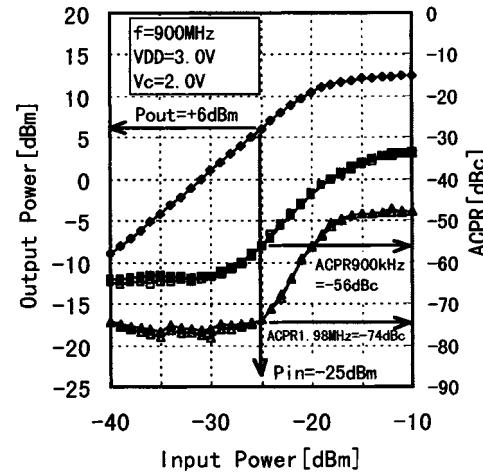

Fig. 9 shows the output power, the ACPR of 900-kHz offset from the carrier, and that of 1.98-MHz offset from the carrier characteristics of the VGA as a function of the input power at VDD and  $V_c$  of 3.0 and 2.0 V, respectively. The VGA indicates output power of +6 dBm, power gain of 31 dB, 900-kHz offset ACPR of -56 dBc and 1.98-MHz offset ACPR of -74 dBc. These performance exhibits the high potential of the VGA for CDMA cellular phone systems.

The performance of the VGA summarized in Table I is sufficient for the CDMA power-amplifier driver.

Fig. 9. Output power, ACPR of 900-kHz offset from the carrier, and that of 1.98-MHz offset from the carrier characteristics of the VGA as a function of the input power, measured at VDD and  $V_c$  of 3.0 and 2.0 V, respectively.

TABLE I

MEASURED PERFORMANCE OF THE

VGA

| Items                                    | Unit | Value      |

|------------------------------------------|------|------------|

| Frequency                                | MHz  | 900        |

| Drain Voltage                            | V    | 3.0        |

| Control Voltage                          | V    | 1.0~2.0    |

| Input Power                              | dBm  | -20        |

| Circuit Current                          | mA   | 28         |

| Power Gain                               | dB   | 31         |

| Dynamic Range<br>( $\pm 1$ dB Linearity) | dB   | 40         |

| ACPR900kHz<br>(Pout = +6 dBm)            | dBc  | $\leq -53$ |

| ACPR1.98MHz<br>(Pout = +6 dBm)           | dBc  | $\leq -74$ |

## V. CONCLUSION

A new VGA MMIC with a wide dynamic range and low-voltage operation linear attenuation circuit designed for a CDMA cellular phone has been successfully developed. Wide dynamic range of 40 dB under a low control voltage of 2.0 V, compatible with high linearity of  $\pm 1$  dB and low ACPR of -53 dBc, which is essential for CDMA, is realized by the new gain control technique. It greatly contributes to the high performance and small size of RF transmission circuits for cellular handsets. We believe that the new gain control technique will apply to the VGA for next-generation cellular phones such as International Mobile Telecommunication 2000 (IMT2000) cellular phone systems.

## ACKNOWLEDGMENT

The authors thank S. Umebachi and M. Nishiuma for their continual encouragement throughout this work. The authors are also grateful to T. Tambo, M. Nakayama, and N. Yoshida for useful discussion and technical assistance.

## REFERENCES

- [1] K. Motoyoshi, T. Tambo, K. Tara, and M. Hagio, "A new low-noise, low-distortion and low-power-consumption variable gain amplifier for digital cellular phones," in *GaAs IC Symp. Tech. Dig.*, 1996, pp. 215-218.

- [2] K. Miyatsuji and D. Ueda, "A low-distortion GaAs variable attenuator IC for digital mobile communication system," in *ISSCC Tech. Dig.*, 1995, pp. 42-43.

- [3] M. Cardullo, E. Douglas, M. Goff, J. Griffiths, K. Harrington, J. Kaiser, S. LeSage, and R. Pengelly, "Transmitter chips for use in a dual-mode AMPS/CDMA chip set," *Microwave J.*, vol. 39, no. 3, pp. 60-72, Mar. 1996.

- [4] V. Aparin, K. Gard, G. Klemens, and C. Persico, "GAAS RFICS for CDMA/AMPS dual-band wireless transmitters," in *IEEE RFIC Symp. Dig.*, 1998, pp. 249-252.

- [5] G. Lizama, T. Andrade, and R. Benton, "1-6 GHz GaAs MMIC linear attenuator with integral drivers," in *IEEE Microwave Millimeter-Wave Monolithic Circuits Symp. Dig.*, 1987, pp. 105-107.

- [6] B. Maoz, "A novel, linear voltage variable MMIC attenuator," *IEEE Trans. Microwave Theory Tech.*, vol. 38, pp. 1675-1683, Nov. 1990.

**Masahiko Inamori** received the B.S. and M.S. degrees from Meijo University, Aichi, Japan, in 1993 and 1995, respectively, both in electronic engineering.

In 1995, he joined the Discrete Device Division, Matsushita Electronics Corporation, Kyoto, Japan, where he has been engaged in development of GaAs MMIC's for cellular phone systems.

**Kaname Motoyoshi** received the B.S. degree in electrical engineering from Kyoto University, Kyoto, Japan, in 1986.

In 1986, he joined the Discrete Device Division, Matsushita Electronics Corporation, Kyoto, Japan, where he has been involved in development of GaAs devices.

**Takahiro Kitazawa** received the B.S. and M.S. degrees from Osaka University, Osaka, Japan, in 1994 and 1996, respectively, both in material physics.

In 1996, he joined the Discrete Device Division, Matsushita Electronics Corporation, Kyoto, Japan, where he has been engaged in development of GaAs MMIC's for cellular phone systems.

**Katsushi Tara** received the B.S. and M.S. degrees from Osaka City University, Osaka, Japan, in 1980 and 1982, respectively, both in applied physics.

In 1982, he joined the Matsushita Electronics Corporation, Kyoto, Japan, where he has been involved in development of GaAs devices. He is currently the Manager of the Development Department, Discrete Device Division.

Mr. Tara is a member of the Institute of Electrical, Information and Communication Engineers (IEICE), Japan, and the Japan Society of Applied Physics

**Masahiro Hagio** received the B.S. degree in electrical engineering and Ph.D. degree in electronics engineering from Kyoto University, Kyoto, Japan, in 1973 and 1993, respectively.

In 1975, he joined the Matsushita Electronics Corporation, Kyoto, Japan, where he has been involved in research and development of GaAs devices. He is currently the General Manager of the Development Department, Discrete Device Division.

Mr. Hagio is a member of the Institute of Electrical, Information and Communication Engineers (IEICE), Japan.