# Modeling, Analysis, and Design of RF LDMOS Devices Using Harmonic-Balance Device Simulation

F. M. Rotella, *Member, IEEE*, G. Ma, Z. Yu, *Senior Member, IEEE*, and R. W. Dutton, *Fellow, IEEE*

**Abstract**—This paper describes how device simulation may be used for the modeling, analysis, and design of radio-frequency (RF) laterally diffused metal-oxide-semiconductor (LDMOS) transistors. Improvements to device analysis needed to meet the requirements of RF devices are discussed. Key modeling regions of the LDMOS device are explored and important physical effects are characterized. The LDMOS model is compared to dc and small-signal ac measurements for calibration purposes. Using the calibrated model, large-signal accuracy is verified using harmonic distortion simulation, and intermodulation analysis. Predictive analysis and a study of the structure's parasitic components are also presented. Load-pull simulation is used to analyze matching network effects to determine the best choices for device impedance matching.

## I. INTRODUCTION

OVER THE past two decades, device simulators such as PISCES (i.e., Medici, Atlas, etc.) have played an important role in understanding device design, physics, and performance [1]–[3]. Specifically, the evolution of PISCES has resulted in new models for physics in order to accurately model the intrinsic device (e.g., [4]), more advanced boundary conditions to represent the matching networks around the device (e.g., [5]), and improved numerics to achieve faster simulations with more complex structures (e.g., [6]).

Recent changes to PISCES include additions to allow for the simulation of RF devices [26]. A harmonic-balance (HB) solver was developed to solve for the large-signal steady-state performance of a semiconductor device rather than using computationally more expensive transient analysis [7]–[9]. Instead of solving for the time samples of each variable, the HB approach expands each device variable (i.e.,  $\Psi$ ,  $n$ , and  $p$ ) as a Fourier series and solves for the coefficients  $X_{n0}$ ,  $X_{nh}^R$ , and  $X_{nh}^I$  given by

$$x_n(t) = X_{n0} + \sum_{h=1}^H (X_{nh}^R \cos(\omega_h t) - X_{nh}^I \sin(\omega_h t)). \quad (1)$$

Manuscript received January 14, 1999. The work of F. M. Rotella was supported by the Semiconductor Research Corporation under Contract SRC 97-SJ-116.

F. M. Rotella was with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA. He is now with Conexant Systems Inc., Newport Beach, CA 92660 USA.

G. Ma is with Motorola, Tempe, AZ 85284 USA.

Z. Yu and R. W. Dutton are with the Department of Electrical Engineering, Stanford University, Stanford, CA 94305 USA.

Publisher Item Identifier S 0018-9480(00)04662-7.

The number of harmonics is limited to  $H$ , where higher order frequency components are assumed to be insignificant. Upon computing the value for the Fourier coefficients, the time-domain signal can be assembled from the Fourier expansion.

HB analysis offers computational benefits over transient analysis in certain circumstances. It captures the steady-state performance of a device in the presence of potentially longer time constant phenomena and avoids an excessive number of time steps in multitone analysis. Conversely, the disadvantage of HB analysis is that the matrix of equations increases proportionally to  $2H + 1$ . Given that the device simulation itself requires the solution of large matrices, special algorithms and numerics have been optimized for solving the semiconductor equations using HB techniques [9]. As a result, the user must then make trade-offs in the modeling of the device in order to minimize the size of these matrices and, in turn, reduce the simulation time.

Another recent improvement to PISCES involves the addition of circuit boundary conditions [27]. Tools currently exist for the simultaneous simulation of circuits and devices [5], [10]. However, these tools are targeted for unit cell development rather than discrete component analysis. Therefore, the improved boundary conditions target the simulation of a discrete device where parasitics are important for performance evaluation. Coupling the boundary conditions with HB simulation leads to a powerful tool for RF device simulation including parasitics [11], [12].

Generalized linear circuits are reduced to a set of boundary conditions for the device simulator as follows:

$$\begin{aligned} \text{DC: } & G_{d0}(E_{d0} - V_{d0}) - I_{d0}(\Psi_0, n_0, p_0) = 0 \\ \text{Fundamental: } & G_{d1}(E_{d1} - V_{d1}) - I_{d1}(\Psi_1, n_1, p_1) = 0 \\ \text{Overtones: } & -G_{dh}V_{dh} - I_{dh}(\Psi_h, n_h, p_h) = 0. \end{aligned} \quad (2)$$

These equations relate the unknown voltage at each electrode ( $V_{di}$ ) to the unknown current flowing into the electrode ( $I_{di}$ ). Only one equation is added per electrode to the device matrix, which has little impact on the solution time. Iterations are performed over the entire set of device equations until a self-consistent solution is attained.

Separate equations are included for the dc bias, fundamentals, and overtones. The dc and fundamental components have source terms in the external circuitry given by the ( $E_{di}$ ) terms. The overtones, on the other hand, have no independent sources because the surrounding circuitry is linear, even though the system is globally nonlinear because of the discrete transistor. Hence,

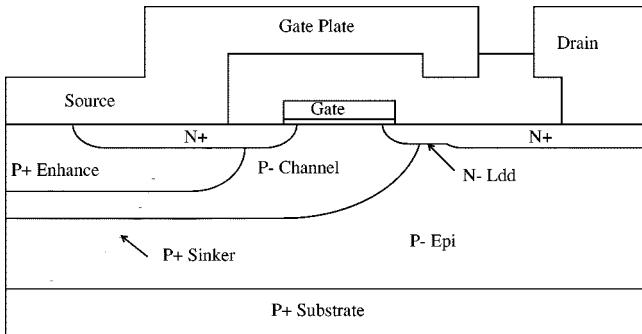

Fig. 1. Cross section of LDMOS device.

the lack of a generating term does not imply that there are no overtones in the external circuitry.

HB analysis and circuit boundary conditions provide PISCES with capabilities for RF device analysis. HB allows for the simulation of the large-signal steady-state performance of a given device structure. External circuit boundary conditions include: 1) the parasitic components; 2) matching networks; and 3) biasing networks that are important to accurately characterize and understand RF behavior. Previous work has used device simulation to characterize the dc and small-signal analysis and required a circuit model to do large-signal analysis [13]. This paper presents an example of modeling, analysis, and design of an RF laterally diffused metal-oxide-semiconductor field-effect transistor (LDMOSFET) by utilizing an integrated device simulation that supports large-signal steady-state analysis, as well as dc and ac effects in a single simulation environment.

## II. LDMOS DEVICE PHYSICS AND MODELING

In order to accurately simulate and model the laterally diffused metal-oxide-semiconductor (LDMOS) device, it is important to understand its operating principles. A cross section of the basic structure is given in Fig. 1. This device was first characterized for RF applications in 1972 by Sigg [14]. The double-diffused design at that time offered advantages because it allowed for channel lengths of  $1 \mu\text{m}$ , while the dominant technology at that time was at  $5 \mu\text{m}$ . With many design advances since 1972, this device offers significant improvements over an equivalent uniform channel MOSFET. For demonstration purposes, a Motorola device built with 0.8 technology is studied [15], [16]. The techniques presented have been applied to next-generation technology development and optimization.

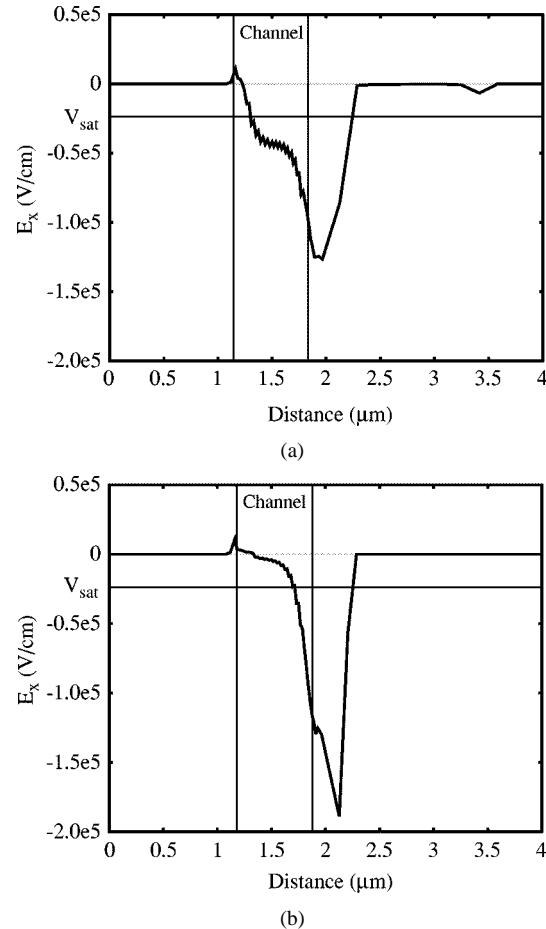

The laterally diffused graded channel enhances RF performance, prevents punch through, and increases the device transconductance. These improvements are a result of increasing the electric field in the channel region such that the electrons reach velocity saturation. Fig. 2(a) and (b) shows a PISCES plot of the longitudinal electric field in the channel of a LDMOS device and a standard MOSFET. The device structures are the same, except in the channel region where device (a) has a graded channel and device (b) has uniform doping. The integrals of the net doping profiles along the interfaces are approximately equal. The devices are biased in inversion just above threshold with 6 V on the drain. The vertical lines indicate the edge of the channel and the minimum

Fig. 2. Comparison of the (a) longitudinal electric field in channel of an LDMOS device versus (b) a standard MOS device. The vertical lines indicate the edges of the channel region and the horizontal line is the approximate electric field ( $2 \times 10^4 \text{ V/cm}$ ) when electrons reach velocity saturation.

electric field to obtain velocity saturation. Electrons reach velocity saturation through the channel region for the graded channel device, but not in the uniformly doped channel.

Improvements to the device include a P+ sinker to connect the source and substrate together also eliminating extra surface bond wires. Thus, only the gate and drain have surface bond wires. The elimination of bond wires on the source leads to improved RF performance in a power amplifier configuration because of the reduced source inductance.

A metal field plate (i.e., Faraday shield) reduces the electric fields at the edge of the gate, thereby increasing the breakdown voltage, reducing hot carrier generation, and reducing  $C_{dg}$ ; however,  $C_{gs}$  increases. In a power amplifier application (common source), the input matching network can compensate for the additional  $C_{gs}$ , while RF performance is improved by reducing the Miller capacitance ( $C_{dg}$ ) between the input (gate) and output (drain). The reduction in the cutoff frequency due to the increased input capacitance is not as critical as long as it is 5–10 times above the operating frequency of the power amplifier.

Other important characteristics include an extended N-lightly doped drain (N-LDD) to decrease the electric field at the drain end of the channel and to optimize  $R_{ds(on)}$ ,  $BV_{dss}$ , and  $C_{dg}$ . As a result, the device is capable of handling the

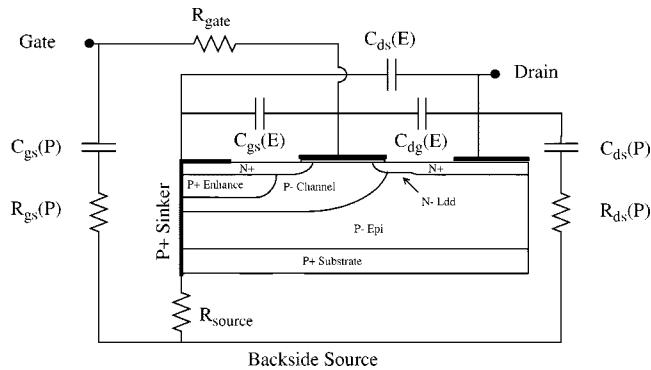

Fig. 3. Model for an LDMOS device used with HB device simulation.

high voltages needed in RF power applications (45 V for the analyzed device).

To use RF device simulation requires modeling and calibration of the intrinsic device and parasitic components. The calibration has the following three goals:

- 1) develop a model for the device that minimizes computational time while maintaining accuracy;

- 2) gain understanding of the device physics affecting the performance;

- 3) obtain better knowledge of the parasitic components and their effect on performance.

Fig. 3 shows the model used to represent the LDMOS device and meets these modeling objectives.

Portions of the device have been eliminated from the physical device structure and replaced with lumped-circuit components in simulation. As a result, the simulation time decreases because the number of mesh nodes is reduced, resulting in a smaller system of equations.

The criterion for replacing a section of the device is based upon the impact of physics surrounding that region. The major regions suitable for replacement in the LDMOS device are the P+ sinker/backside contact and the surface contact structure. The P+ sinker is replaced by an electrode along the source edge of the device to act as a low-resistance path connecting the source and substrate. Rather than simulating the full substrate to the backside contact ( $\sim 230$  mm), a resistance is placed on this contact to represent the current path to the backside.

In addition to the backside contacts, the surface contacts are replaced with circuit components. Fig. 3 shows two contributions, one from the actual device electrode vias (*E*) and the other from the surface pads (*P*). The electrode structure contributes capacitances while the pad structure contains a capacitor and resistor in series. The resistance under the pad adds to the impedance of the circuit branch and becomes important at higher frequencies.

### III. ANALYSIS OF LDMOS STRUCTURE

In this section, the model for the LDMOS structure is characterized and the results are compared to measured data. The key modeling regions addressed in this paper are the source resistance, intrinsic device regions (i.e., channel), and surrounding parasitic components. In addition, self-heating effects are characterized in relation to *I-V* characteristics

Fig. 4. Current flow lines through the P+ sinker and the substrate of an LDMOS device with a backside contact.

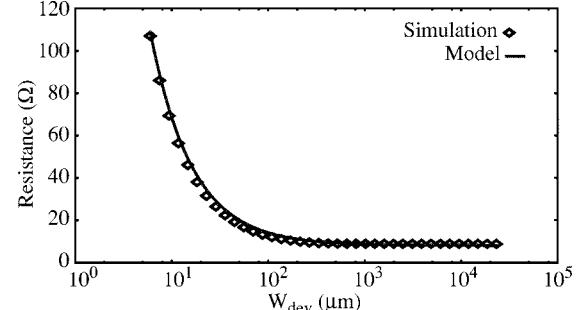

Fig. 5. Source resistance as a function of device width.

and the graded channel effects on the *C-V* characteristics are discussed.

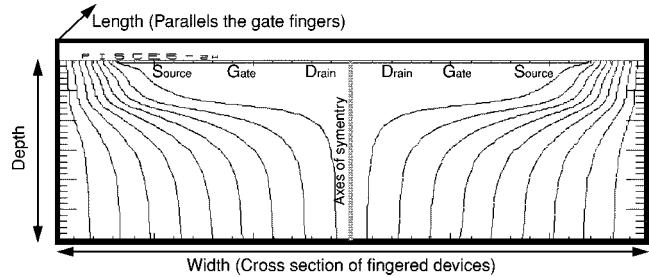

In order to reduce the source inductance, the device structure is designed for a backside contact, which adds to the source resistance. The impact and magnitude of this resistance depends upon the pitch spacing of the fingers in the device layout. The current flows from the drain, through the channel, into the metal contacting the source (and Faraday Shield) and the sinker contact, through the sinker, and spreads into the substrate making its way to the backside contact.

The source resistance has components from the distributed contact resistance, sinker resistance, and substrate resistance. The contact resistance is insignificant compared to the other components for this device structure and, thus, will not be considered. In other structures, this resistance could potentially play an important role and, therefore, it would need to be characterized. A PISCES simulation of the sinker structure leads to the current flow lines shown in Fig. 4. The figure contains a cross section of two adjacent devices due to the fingered layout of the structure. The devices themselves are not included in the simulation since they do not directly affect the results. Instead, the source doping is extended all the way across both devices. The spreading of the current is limited and, thus, there is a significant effect on the actual resistance.

Fig. 5 shows the resistance of one entire sinker as a function of the width of the device. The points represent simulation data and the line is a plot of

$$R(W_{\text{dev}}) = \frac{1}{L_{\text{snk}}} \left( \frac{D_{\text{snk}}}{W_{\text{snk}}} + \frac{D_{\text{sub}}}{W_{\text{max}}} + \frac{D_{\text{sub}}}{W_{\text{dev}}} \right) \frac{1}{\sigma} \quad (3)$$

where  $L_{\text{snk}}$  is the length of the sinker along the surface,  $W_{\text{snk}}$  is the width of the sinker along the surface,  $D_{\text{snk}}$  is the depth of the sinker (contacts the substrate through the P-epi layer),  $D_{\text{sub}}$  is

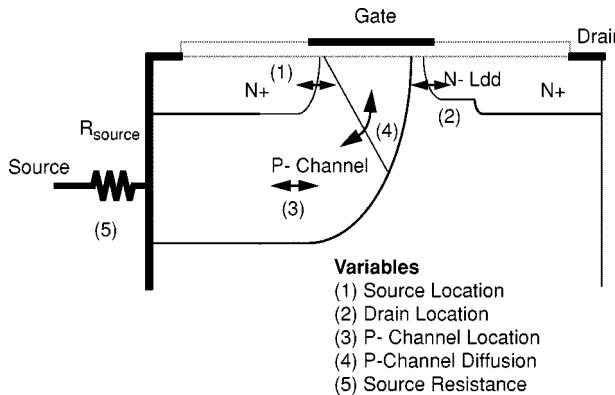

Fig. 6. DOE to determine optimum two-dimensional doping profile.

the thickness of the substrate,  $W_{\max}$  is the maximum spreading of current in the substrate,  $W_{\text{dev}}$  is the width of one device (i.e., abscissa), and  $\sigma$  is the substrate conductances, which is considered valid for the sinker. (If the conductance is significantly different then the sinker, the substrate would have to be divided by their respective individual conductance values.)

Measuring one sinker as an independent unit yields a resistance of  $8 \Omega$ . The simulation model predicts a slightly higher resistance of  $8.5 \Omega$ . When device confinement is included in evaluation of the source resistance, one device sees a source resistance of  $46 \Omega$ . Thus, as the size of the devices are scaled, the source resistance must be reduced appropriately so as not to degrade performance due to an increase of this parasitic component.

The second key modeling region of interest is the graded channel. Only one-dimensional doping profiles are simulated and calibrated with the measured data; however, the profiles must be expanded into two dimensions in order to generate the channel region of the device. The methodology chosen for this calibration is based upon design of experiments (DOE) [17]. Key PISCES parameters describing the two-dimensional spreading of doping profiles are varied based upon manufacturing tolerances (Fig. 6) [18]. The parameters to be varied are: 1) the inner edge of the source and drain relative to the gate poly [(1) and (2) in Fig. 6]; 2) the edge of the P-channel implant relative to the edge of the gate [(3) in Fig. 6]; 3) the curvature of the P-channel region under the gate [(4) in Fig. 6]; and 4) the source resistance [(5) in Fig. 6]. The fitting of the source resistance allows for a comparison with that from the model for the source resistance.

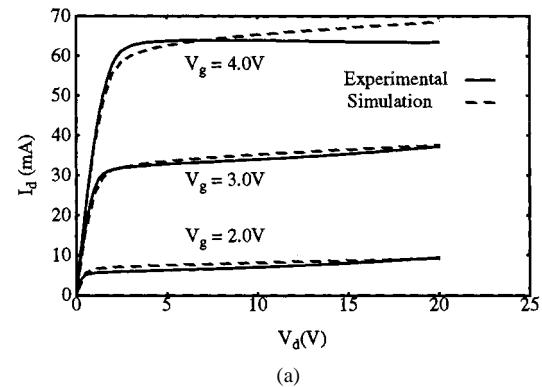

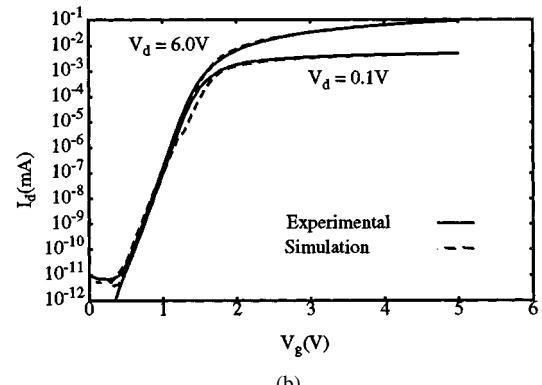

A factorial experiment with the five variables limited by the processing characteristics was run and a statistical model was developed. Three independent statistical dependences relate the threshold voltage, transconductance, and subthreshold slope (i.e., all three being responses) to the process variables. Simulated parameters are determined (i.e., measured "virtually") using the same methods as in the laboratory experiments. Upon generating a statistical model for each of the responses, they are used to determine the optimum set of parameters. The results of that optimization are shown in Fig. 7 where simulated and measured  $I$ - $V$  characteristics are presented.

In addition to calibrating the intrinsic LDMOS model, the statistical models may be used to do sensitivity analysis.

(a)

(b)

Fig. 7. Comparison of simulated and measured  $I$ - $V$  characteristics for LDMOS device.

Sensitivity analysis gives the design engineer understanding of the degree to which a parameter affects the device performance and is useful for optimizing the next generation of the technology.

In this paper, RF power devices are optimized to transmit large signals where signal spikes can generate significant heating.<sup>1</sup> As a result, the device can exhibit a negative differential resistance, as is apparent in the measured drain characteristics shown in Fig. 7(a). The application for which this device is targeted does not require its operation in the region of high currents; thus, the exclusion of self-heating effects should not affect the results at low power levels and the error is less than 10% at high power levels.

Having calibrated and characterized the dc response, small-signal analysis can provide a detailed understanding of device operation. The standard  $C$ - $V$  characteristics are simulated under the same conditions as use in measurements. A dc value is swept while ac perturbations are applied to one contact. The ac current is obtained and the capacitance is computed from the imaginary part of the simulated admittance ( $y$ -parameters).

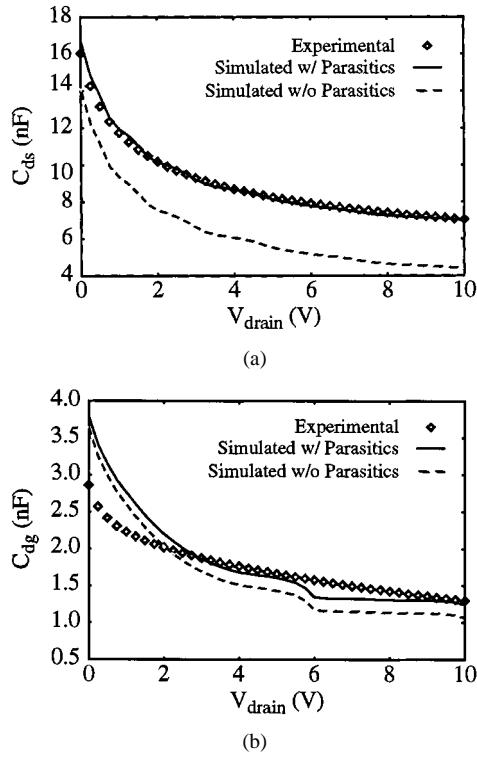

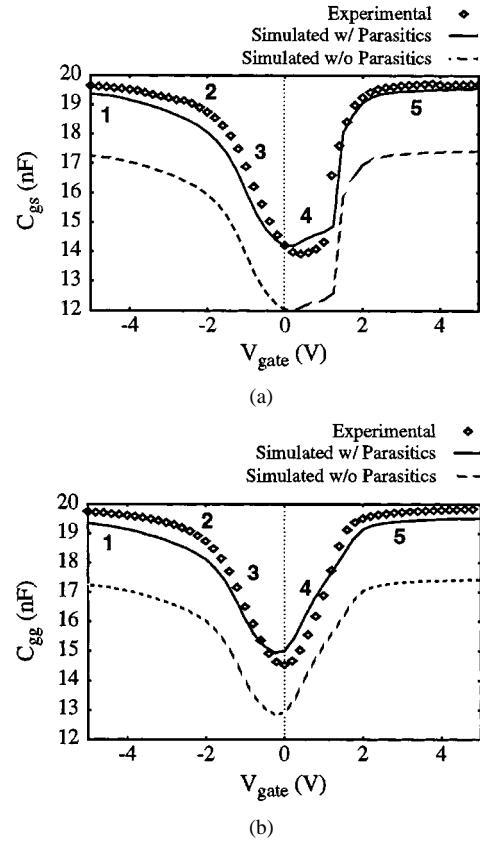

Figs. 8 and 9(a) show the standard  $C$ - $V$  plots for  $C_{dg}$ ,  $C_{ds}$ , and  $C_{gs}$  measured at 1 MHz; the plots show small-signal

<sup>1</sup>Future application of this modeling technique requires two important additions in the model. With increasing power densities, self-heating becomes important and, thus, the model will require that the lattice thermal diffusion equation be solved simultaneously with the semiconductor equations [19]. In addition, breakdown will limit the high-power operation, thus requiring the modeling of impact ionization for devices operated in that region [20], [21]. Both of these effects are computationally complex [1] and require improvements in HB solution techniques [9].

Fig. 8. Measured and simulated capacitance for  $C_{dg}$  and  $C_{ds}$ .

characteristics with and without parasitics. Since specific parasitic components affect each curve independently, their values are adjusted from their initially computed values. For example, the pad impedance can be computed from a one-dimensional PISCES simulation of the structure.

In addition, the  $C-V$  measurements can provide detailed information about the channel region. Fig. 9(a) and (b) shows two forms of measurements for  $C_{gs}$  (drain floating) and  $C_{gg}$  (drain and source grounded), respectively. Starting with a negative  $V_{gs}$  in Region 1, the channel is in accumulation. With increasing  $V_{gs}$ , the drain side of the device enters depletion, the source side is in accumulation, and the center of the channel is at flat-band for tens of millivolts (Region 2). As the gate voltage continues to increase, the depletion layer reduces the capacitance until around  $V_{gs} = 0$  V (Region 3). At this point, the drain side of the device enters inversion (Region 4). When measuring  $C_{gs}$ , there is no current path through the drain-side inversion layer and the capacitance stays low. When measuring  $C_{gg}$ , there is a drain inversion bypass capacitance in parallel with the source-side depletion capacitance. Since the inversion capacitance is large and the inversion layer moves across the channel from drain to source side, the net capacitance measurement increases with voltage as the inversion layer moves across the channel. When the source side of the channel inverts,  $C_{gs}$  immediately switches to the inversion capacitance, whereas  $C_{gg}$  had slowly approached that value. Pieracci *et al.* have used this property of the graded channel device in order to estimate doping profile based upon the incremental threshold voltage [22].

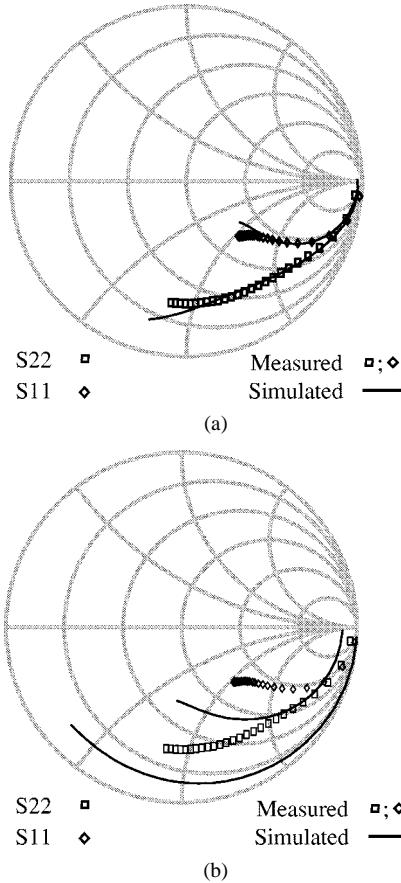

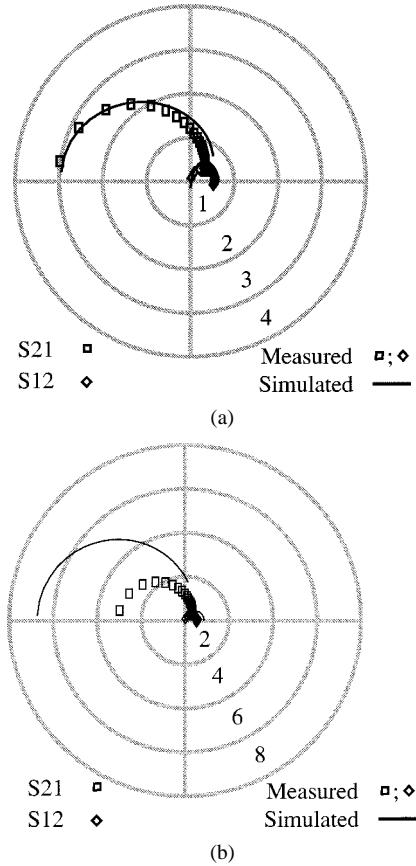

$S$ -parameters provide an evaluation of the high-frequency accuracy of the model. Due to the difficulty in measuring the full multicell device, a single cell of the structure is measured and compared to a single-cell model. The device is biased under

Fig. 9. Measured and simulated values for  $C_{gs}$  and  $C_{gg}$  to allow for analysis of graded channel region.

the typical conditions for its targeted application. The measured  $S$ -parameters match the simulated  $S$ -parameters up to about 6 GHz, which encompasses up to the seventh-order harmonic for the 850-MHz application. Figs. 10 and 11 show that the parasitic components contribute significantly to the impedances looking into the device and lead to a degradation in the small-signal gain of the structure. Hence, layout optimization and reduction of parasitic components is a key design factor in developing next-generation technology.

#### IV. EVALUATION OF DEVICE RF PERFORMANCE

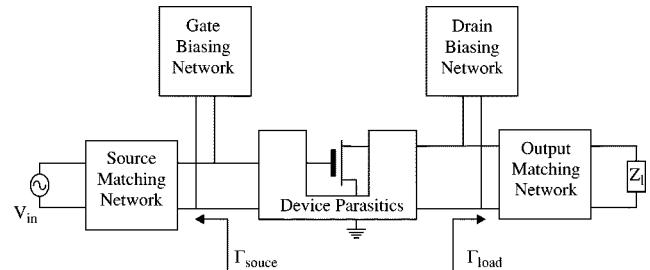

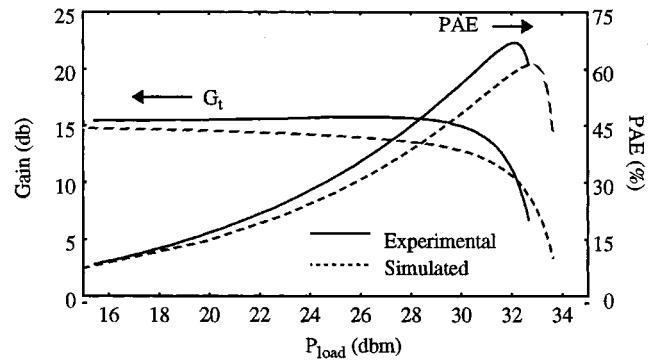

The previous sections described how the intrinsic device simulation and parasitic analysis can be used to better understand performance tradeoffs. In this section, the model is used to evaluate RF performance for the measurement setup shown in Fig. 12. The RF performance gauges include the transducer gain ( $G_t$ ), power-added efficiency (PAE), and intermodulation distortion (IMD).

For single-tone harmonic-distortion analysis, a large-signal sinusoid is applied at the input to the power device ( $V_{in}$ ) and the steady-state large-signal response is computed numerically. The transducer gain and PAE characterize the performance of the device. The gain is given by

$$G = 10 \log \left( \frac{P_{load}}{P_{avs}} \right) \quad (4)$$

which takes the ratio of the output power delivered to the load and the power available from the source ( $P_{avs}$ ). The PAE gives

Fig. 10. LDMOS impedances looking into the device: (a) with and (b) without parasitic components.

the percentage of power that goes into amplification of the signal and is given by

$$\text{PAE} = \left( \frac{P_{\text{load}} - P_{\text{avs}}}{I_{\text{avg}} V_{\text{dc}}} \right) \times 100\%. \quad (5)$$

Fig. 13 compares the simulated gain and efficiency with experimental data for an input frequency of 850 MHz using matching networks optimized for the device application (refer to Section V). The gain and efficiency are plotted versus the output power ( $P_{\text{load}}$ ) since the power amplifier has to meet a minimum output power specification for the cell phone industry standard. The gain at low power is equivalent to the small-signal gain. At an input power of  $-30$  dBm, the simulated response of 15.1 dB agrees well with the measured small-signal response of 15.4 dB. The gain rolls off at higher power levels because the device operates in  $g_m$  compression and the output power is limited by the saturation current. The efficiency is low for small  $P_{\text{load}}$  because the device drains more power due to Class-A operation. Efficiency increases until just after the gain starts to roll off. At this point,  $P_{\text{avs}}$  approaches  $P_{\text{load}}$ , resulting in very little power added to the input signal.

Although the curves differ depending on the specific region of operation, the two results show an overall good agreement consistent with several factors that can affect the results. The strongest influencing factor is that of the matching networks. The matching networks used in the simulation are those determined experimentally by a load-pull system.

Fig. 11. LDMOS gain: (a) with and (b) without parasitic components.

Fig. 12. Configuration of a power amplifier. The biasing networks set the load lines and the matching networks provide for transfer of RF power.

Fig. 13. Simulated and measured RF responses for gain and efficiency of a power amplifier.

(Section V discusses simulated load-pull analysis.) In spite of a good match for the  $I$ - $V$  and  $C$ - $V$  characteristics, this matching

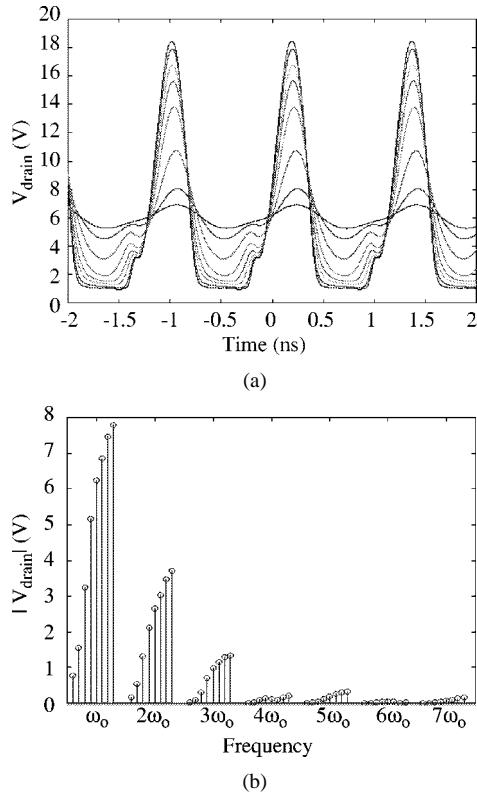

Fig. 14. (a) Time-domain signal and (b) frequency spectrum of the drain voltage in a harmonic-distortion large-signal sinusoidal simulation. The larger magnitude of the signal indicates increasing power along the gain curve.

network is optimized for the manufactured device used in the measurement with all of its inherent process variations and not the specific device in the model.<sup>2</sup> In addition to the matching network, the gain rolloff is associated with the edge of the linear and saturation region as the device enters  $g_m$  compression (i.e., high drain current and high gate voltage). Under this condition, the device exhibits self-heating, thus causing degradation in performance. As stated previously, the simulator neglects these self-heating effects and, thus, overpredicts the performance by about 10%.

Using the results of the HB device simulation, it is possible to examine the signals in the time domain as well as their associated spectra. Fig. 14 shows the drain voltage in both the time and the frequency domains for increasing power. At low-voltage levels, the device operates in Class A. As the power level increases, the voltage cannot swing below threshold and, thus, enters Class-AB operation. As the power level continues to increase, the drain voltage is limited by  $g_m$  compression and, thus, the upper swing becomes limited. The spectrum exhibits this effect as higher order frequency components become more apparent.

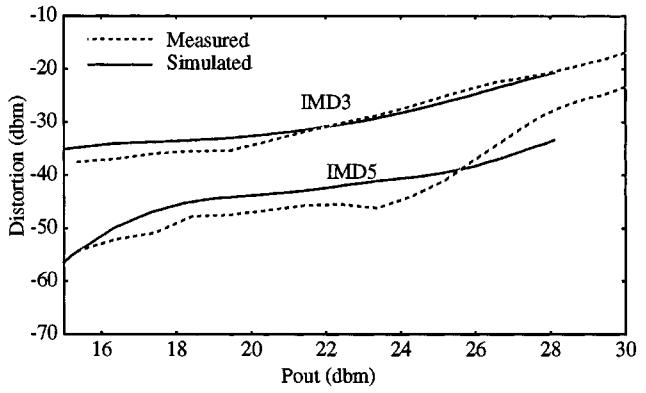

IMD provides a way to characterize linearity of the device when two closely spaced tones are applied in the frequency domain. Harmonics are not only created at multiples of the frequencies, but also at integer sums and differences of the frequen-

Fig. 15. Simulated and measured IMD of the power amplifier.

cies. This leads to the generation of a harmonic in the baseband, which cannot be filtered. The amount of IMD is characterized by computing the ratio of power in the generated harmonics referenced to the fundamentals.

Using an eighth-order simulation, the IMD for the third- and fifth-order harmonics are computed for simulation frequencies of  $f_1 = 851$  MHz and  $f_2 = 849$  MHz. The simulated results are compared to experimental data in Fig. 15, showing good qualitative and quantitative agreement.

## V. PREDICTIVE ANALYSIS AND OPTIMIZATION

Having verified the RF performance of the physical model, it is now possible to use simulation to evaluate performance in design variations and process control. Since parasitic components are important in the device performance, this section examines those components through process variations and the matching networks required for optimum power transfer.

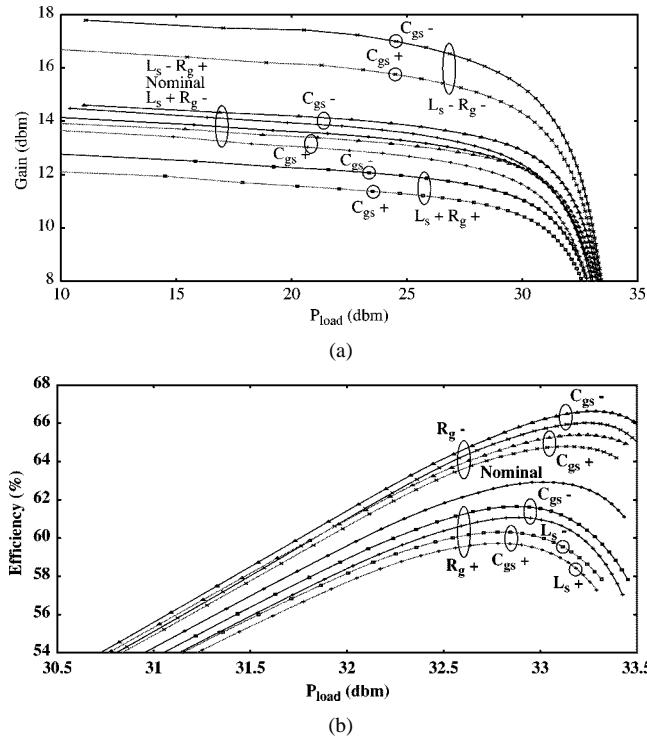

Knowing which parasitics have the largest impact on the performance can lead to judicious selection of the parasitics for subsequent design optimization. A DOE is used to analyze the impact of three components at their high and low values as observed in manufacturing.  $R_g$  is selected because it is determined by the silicide processing step and, hence, can be adjusted.  $C_{\text{gs}}$  is related to the Faraday shield of the device and the value of  $L_s$  (source inductance) is difficult to model physically due to back-side contact effects.

The effects of the parasitic components on gain and efficiency are shown graphically in Fig. 16. The general effects of the parasitic components on the amplifier performance are apparent, but the important observations come from the degree to which these parasitics affect the performance. In the gain curves, both  $R_g$  and  $L_s$  have a similar impact within the limits chosen for these parameters. When both parameters are at the high level, the gain is the lowest, and likewise when both are at their low levels, the gain reaches its highest value. When one increases and the other decreases, very little improvement is observed.  $C_{\text{gs}}$  has only a minor impact on the gain and “modulates” the curve about the solution established by  $R_g$  and  $L_s$ . The efficiency curves clearly show that the strongest effect can be attributed to the gate resistance.  $C_{\text{gs}}$  has the next strongest effect and  $L_s$  has the least impact on performance.

<sup>2</sup>In actual power amplifier circuits, it is often necessary to provide a variable resistor or capacitor on the circuit board to provide for tuning of the matching networks and other resonant circuits in order to meet the manufacturing specifications.

Fig. 16. Simulated effects of parasitic components on the gain and efficiency of the LDMOS device. The + and - indicate whether the variable is at its manufacturing high or low value.

In addition to the parasitics components considered above, an RF device engineer can also modify the intrinsic device structure to address improvements as technology evolves. Sato-Iwanga shows that by using a similar modeling approach the intermodulation components of a MESFET can be studied [23]. Jang shows the importance of mixed circuit and device simulation for RF performance analysis of bipolar junction transistors (BJT's) [24].

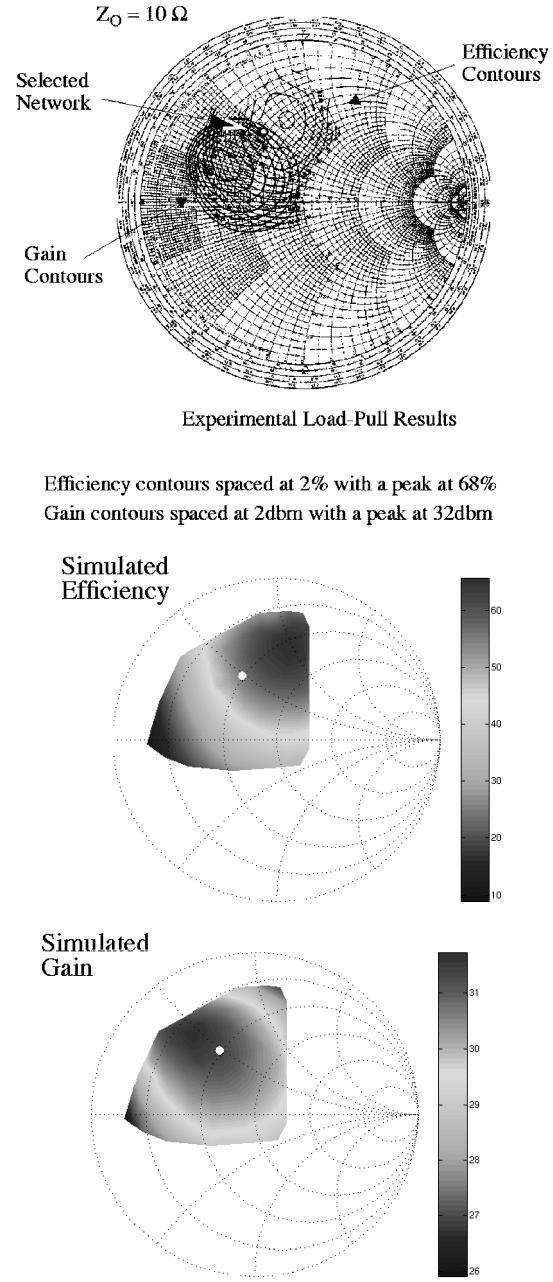

Gain, efficiency, and linearity are affected by the matching networks in the circuit. An application for this device requires that gain meets a minimum specification and efficiency is maximized for the application. Input and output matching networks have limited interactions with each other and are, thus, tuned independently. The input matching network is tuned to minimize reflections back to the signal source using a best guess for the output matching network. To determine the best output matching network, the reflection coefficient looking toward the load ( $\Gamma_{load}$  in Fig. 12) is varied by sweeping the load across a range of values where the best response is expected (i.e., a load-pull) [25]. For each matching network, the gain and efficiency are measured for a constant input power of 20 dBm and plotted over the range of the network's reflection coefficients.

Fig. 17 shows experimental contour plots for gain and efficiency on a Smith chart that is used to represent the different reflection coefficients. (Note that the impedances on the Smith chart are normalized to  $10\ \Omega$  rather than the standard  $50\ \Omega$  to obtain greater visibility.) The white point on the graph indicates the matching network used to generate the earlier plots of gain and efficiency. The selection criteria for this point depends upon the application for the device. The alignment of the maxima and

Fig. 17. Comparison of experimental and simulated load-pull analysis. The darken point represents the matching network used in the earlier RF response.

the shape of the contours demonstrate that the simulated results (Fig. 17) agree with the experimental data.

There are some important criteria for load-pull simulations. Load-pull equipment is designed to optimize the impedance for a specific reflection coefficient given that it can be realized by different combinations of physical components. In simulation, the matching network is specified with physical components based upon the layout of the fixture for the application in which the device is utilized. If the physical components are chosen poorly, reflections back into the device or filtering may affect the performance of the device through higher order harmonics. Hence, care has been taken so that the choice of components

maximizes the performance of the device for a given reflection coefficient of the output matching network.

## VI. CONCLUSIONS

This paper discussed the modeling, analysis, and design of LDMOS transistors using advance device simulation. Improvements to the PISCES tool allow for large-signal steady-state analysis (HB) and the inclusion of parasitic components in those simulations. The LDMOS structure is modeled and calibrated based on  $I$ - $V$  and  $C$ - $V$  data. This analysis also leads to a more detailed understanding of the underlying device performance and physics. With the calibrated model, RF performance curves for large-signal gain, efficiency, and linearity of the LDMOS model are verified. This paper presents a number of simple design examples, yet the methodology employed can be easily expanded to more critical design analysis and ultimately support shorter design cycles.

## ACKNOWLEDGMENT

The authors thank B. Troyanovsky, Hewlett-Packard Company, Santa Rosa, CA, for major contributions in the development of a HB solver for device simulation. The authors further thank R. Pearl, Motorola, Tempe, AZ, T. Spoonhunter, Motorola, Tempe, AZ, M. Shields, Motorola, Tempe, AZ, and E. Johnson, Motorola, Tempe, AZ, for technical support and measurement data.

## REFERENCES

- [1] Z. Yu, D. Chen, L. So, S. Beebe, R. Goossens, F. Rotella, and R. Dutton, *Pisces 2ET with Applications Documentation*. Stanford, CA: Leland Stanford Junior Univ., 1994.

- [2] *Medici User's Manual*, Technology Modeling Assoc., Palo Alto, CA, 1996.

- [3] *Atlas Users Manual*, Silvaco Int., Santa Clara, CA, 1996.

- [4] C. Lombardi, S. Manzini, A. Saporito, and M. Vanzi, "A physically based mobility model for numerical simulation on nonplanar devices," *IEEE Trans. Computer-Aided Design*, vol. 7, pp. 1042–1048, Nov. 1988.

- [5] G. J. Rollins and J. Choma, "Mixed-mode PISCES-SPICE coupled circuit and device solver," *IEEE Trans. Computer-Aided Design*, vol. 7, pp. 862–867, Aug. 1988.

- [6] N. Aluru, K. Law, and R. Dutton, "Advances in numerical methods for convective hydrodynamic model of semiconductor devices," in *SISDEP Tech. Dig.*, Erlangen, Germany, Sept. 1995, pp. 86–89.

- [7] B. Troyanovsky, Z. Yu, L. So, and R. Dutton, "Relaxation-based harmonic balance technique for semiconductor device simulation," in *ICCAD Tech. Dig.*, San Jose, CA, Nov. 1995, pp. 700–703.

- [8] B. Troyanovsky, Z. Yu, and R. Dutton, "Large signal frequency domain device analysis via the harmonic balance technique," in *SISDEP Tech. Dig.*, Erlangen, Germany, Sept. 1995, pp. 114–117.

- [9] B. Troyanovsky, "Frequency domain algorithms for simulating large signal distortion in semiconductor devices," Ph.D. dissertation, Dept. Elect. Eng., Stanford Univ., Stanford, CA, 1997.

- [10] B. Mayaram, B. Kartikeya, and D. O. Pederson, "Coupling algorithms for mixed-level circuit and device simulation," *IEEE Trans. Computer-Aided Design*, vol. 10, pp. 1003–1012, Aug. 1992.

- [11] B. Troyanovsky, F. Rotella, Z. Yu, R. Dutton, and J. Sato-Iwanga, "Large signal analysis of RF/microwave devices with parasitics using harmonic balance device simulation," in *SASIMI Tech. Dig.*, Fukuoka, Japan, Nov. 1996.

- [12] F. Rotella, B. Troyanovsky, Z. Yu, R. Dutton, and G. Ma, "Harmonic balance device analysis of an LDMOS RF power amplifier with parasitics and matching network," in *SISPAD Tech. Dig.*, Boston, MA, Sept. 1997, pp. 157–159.

- [13] P. Perugupalli, M. Trivedi, M. Kshenai, and S. K. Leong, "Modeling and characterization of an 80 V silicon LDMOSFET for emerging RFIC applications," *IEEE Trans. Electron Devices*, vol. 45, pp. 1468–1478, July 1998.

- [14] H. J. Sigg, G. D. Vendelin, T. P. Cauge, and J. Kocsis, "D-MOS transistor for microwave applications," *IEEE Trans. Electron Devices*, vol. ED-19, pp. 45–54, Jan. 1972.

- [15] G. Ma, W. Burger, C. Dragon, and T. Gillenwater, "High efficiency LDMOS power FET for low voltage wireless communications," in *IEDM Tech. Dig.*, San Francisco, CA, Dec. 1996, pp. 91–94.

- [16] A. Wood, C. Dragon, and W. Burger, "High performance silicon LDMOS technology for 2-GHz RF power amplifier applications," in *IEDM Tech. Dig.*, San Francisco, CA, Dec. 1996, pp. 87–90.

- [17] D. C. Montgomery, *Design and Analysis of Experiments*, 4th ed. New York: Wiley, 1997.

- [18] S. Wolf and R. N. Tauber, *Silicon Processing for the VLSI Era*. Sunset Beach, CA: Lattice Press, 1986, vol. 1–3.

- [19] R. Stratton, "Semiconductor current-flow equations (diffusion and degeneracy)," *IEEE Trans. Electron Devices*, vol. ED-19, pp. 1288–1292, Dec. 1972.

- [20] W. Haensch and M. Miura-Mattausch, "The hot-electron problem in small semiconductor devices," *J. Appl. Phys.*, vol. 60, no. 2, pp. 650–656, July 1986.

- [21] J. W. Slotboom, G. Streutker, M. J. v. Dort, P. H. Woerlee, A. Pruijboom, and D. G. Gravestijn, "Non-local impact ionization in silicon devices," in *IEDM Tech. Dig.*, Washington, DC, Dec. 1991, pp. 127–130.

- [22] A. Pieracci, M. Lanzoni, P. Galbiati, S. Manzini, C. Contiero, and B. Ricco, "Extraction of channel doping profile in DMOS transistors," in *IEDM Tech. Dig.*, San Francisco, CA, Dec. 1996, pp. 485–488.

- [23] J. Sato-Iwanga, K. Fujimoto, H. Masato, Y. Ota, K. Inoue, B. Troyanovsky, Z. Yu, and R. W. Dutton, "Distortion analysis of GaAs MESFET's based on physical model using PISCES-HB," in *IEDM Tech. Dig.*, San Francisco, CA, Dec. 1996, pp. 163–166.

- [24] J. Jang, E. Kan, L. So, and R. Dutton, "Parasitic characterization of radio-frequency (RF) circuits using mixed-mode simulation," in *Proc. Custom Integrated Circuits Conf.*, San Diego, CA, May 1996, pp. 445–448.

- [25] J. Cusak, S. Perlow, and B. Perlman, "Automatic load contour mapping for microwave power transistors," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-22, pp. 1146–1152, Dec. 1974.

- [26] F. Rotella, B. Jroyanovsky, Z. Yu, and R. Dutton, *Supplemental Manual for PISCES-2HB: Circuit Boundary Conditions and Harmonic Balance Module*. Stanford, CA: Leland Stanford Junior Univ., 1999.

- [27] F. Rotella, "Mixed Circuit and device simulation for analysis, design, and optimization of opto-electronic, radio frequency, and high speed semiconductor devices," Ph.D. dissertation, Dept. Elect. Eng., Stanford Univ., Stanford, CA, 2000.

**F. M. Rotella** (S'86–M'98), photograph and biography not available at time of publication.

**G. Ma**, photograph and biography not available at time of publication.

**Z. Yu** (S'80–M'80–SM'94), photograph and biography not available at time of publication.

**R. W. Dutton** (S'67–M'70–SM'80–F'84), photograph and biography not available at time of publication.