# Design and Performance of a *Ka*-Band Monolithic Phase Shifter Utilizing Nonresonant FET Switches

Kenichi Maruhashi, *Member, IEEE*, Hiroshi Mizutani, *Member, IEEE*, and Keiichi Ohata, *Member, IEEE*

**Abstract**—This paper describes design consideration and performance of a *Ka*-band monolithic phase shifter utilizing nonresonant FET switches. The switches show broad-band on/off characteristics up to 60 GHz without using inductors; thus, robust circuit design is possible for a switched-line phase shifter. To determine circuit topology, we introduce a schematic design approach. As a result, desired phase shift as well as good matching characteristics can be realized. The developed 4-bit monolithic phase shifter demonstrates an overall phase deviation less than 5° rms and an insertion loss variation less than 0.65 dB rms from 33 to 35 GHz. For all 16 states, the insertion loss is measured to be  $13.1 \pm 1.1$  dB and the VSWR is less than 1.6. The chip size of the monolithic phase shifter is 2.5 mm × 2.2 mm.

**Index Terms**—Millimeter-wave phase shifter, MMIC's, MMIC phase shifters, MODFET switches.

## I. INTRODUCTION

PHASE shifters are key components for phased-array antenna systems. Monolithic implementation is necessary for low cost and high producibility. Several monolithic phase shifters have been reported at *Ka*- and *Q*-bands [1]–[3]. In these frequency bands, switched-line configuration has advantages of applicable phase-shift characteristics to the above systems and small chip size due to simple circuit and layout designs. FET switches are advantageous over their p-i-n diode counterparts [4] for a simple epitaxial structure and a small number of fabrication steps in the monolithic integrated-circuit (IC) process, and for negligible current to drive switches.

A conventional switched-line phase shifter at *Ka*-band employs resonant switches, which consist of FET's and spiral inductors [1], [2]. In order to obtain good isolation characteristics for the off-state switch, a precise model or well-established data base for the inductors is needed at the operating frequency. Moreover, for a relatively wide-band phase shifter, eliminating resonance is desirable for reduced sensitivity to process variation and design tolerance. However, at *Ka*-band, it had been difficult to achieve sufficient isolation for the FET switches without resonance, due to parasitics. Recently, we have developed a nonresonant FET switch operating from dc to 60 GHz [5], [6]. Based on ohmic electrode sharing technology (OEST), parasitics around the switch have been reduced. The size of the switch is almost as small as that of an FET having

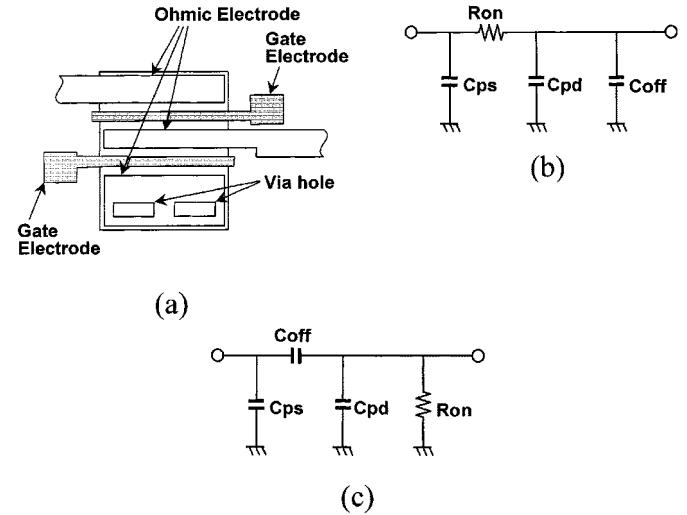

Fig. 1. OEST switch. (a) Layout pattern. (b) On-state equivalent circuit. (c) Off-state equivalent circuit.

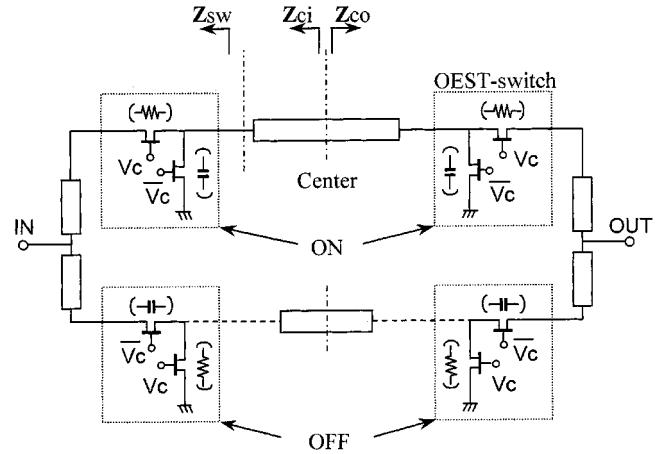

Fig. 2. Circuit scheme for a switched-line phase shifter.

same gatewidth, indicating that the developed switch is suitable for monolithic phase shifters.

In this paper, we demonstrate the design process and performance of a *Ka*-band monolithic phase shifter using the OEST switches. The fabricated switched-line phase shifter shows good phase-shift characteristics with high design feasibility.

## II. CIRCUIT DESIGN

A layout and on- and off-state equivalent circuits of the OEST switch are shown in Fig. 1. The switch consists of cascade-connected series and shunt FET's. Reduction of parasitic induc-

Manuscript received September 18, 1998.

K. Maruhashi and K. Ohata are with the Photonic and Wireless Devices Research Laboratories, System Devices and Fundamental Research, NEC Corporation, Shiga 520-0833 Japan (e-mail: k-maruhashi@bl.jp.nec.com).

H. Mizutani is with the System ULSI Development Division, NEC Corporation, Kanagawa 211-0011, Japan.

Publisher Item Identifier S 0018-9480(00)06530-3.

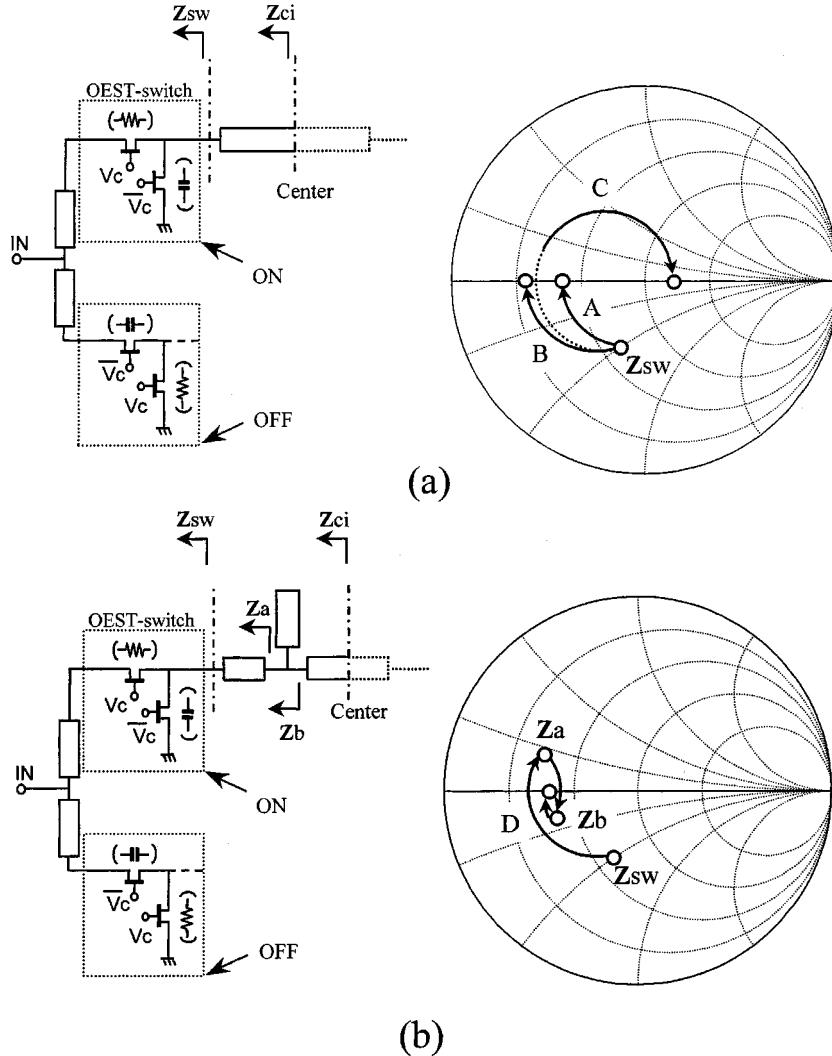

Fig. 3. Impedance responses: (a) when the reference lines and the delay lines of the 22.5°- and 180°-bit phase shifters and (b) when the delay line of the 90°-bit phase shifter are added to the switches.

tance and capacitance has been realized by arraying both FET's with a common electrode between them instead of using conventional wiring. This resulted in broad-band on/off characteristics up to 60 GHz without using inductors [5], [6]. The switches have small on-state series resistance ( $R_{on}$ ) and small off-state series capacitance ( $C_{off}$ ), which are essential for low insertion loss and high isolation, respectively. Over dc–40 GHz, the measured insertion loss was better than 1.5 dB and the isolation was larger than 22 dB. The switch power capability larger than 20 dBm has been reported at 40 GHz [6].

A circuit scheme for a switched-line phase shifter is shown in Fig. 2. The signal path is switched in order to obtain phase shift owing to the length difference between reference and delay lines. In phase-shifter design, two conditions must be satisfied. One is the matching condition and the other is the phase-shift condition. Since the OEST switches appear as capacitance connected between the line and ground, mismatch will occur. To obtain good phase shift and matching characteristics, a special design technique has been introduced as follows. Dividing the circuit shown in Fig. 2 at center, we define the impedance viewing from the center to input port as  $Z_{ci}$ , and the impedance viewing

from the center to output port as  $Z_{co}$ . At this design step, lossless circuits are assumed and, therefore, matching condition is expressed as  $Z_{ci} = Z_{co}^*$ . Since  $Z_{ci}$  is identical to  $Z_{co}$  due to circuit symmetry,  $Z_{ci}$  (or  $Z_{co}$ ) should be real ( $\text{Im}(Z_{ci}) = 0$ ) and plotted on the  $X$ -axis in the Smith Chart. For a half-set of the divided circuit in Fig. 2, the phase-shift condition is that the phase should delay half of the desired phase shift for a whole phase shifter.

The circuit topology can be found using a schematic design concept as follows. The impedance responses are shown in Fig. 3(a) when the reference line for each single-bit phase shifter and the delay lines of the 22.5°- and 180°-bit phase shifters are added to the switches. The impedance  $Z$  is described as

$$Z = \frac{Z_{sw} \cos \theta + j Z_0 \sin \theta}{\cos \theta + j(Z_{sw}/Z_0) \sin \theta} \quad (1)$$

where  $Z_{sw}$  is the impedance viewing into the output of the switch (see Fig. 2), and  $Z_0$  and  $\theta$  are characteristic impedance and electrical length in angle unit of the line.  $Z_{sw}$  has a negative imaginary value due to the capacitive nature of the switch. For

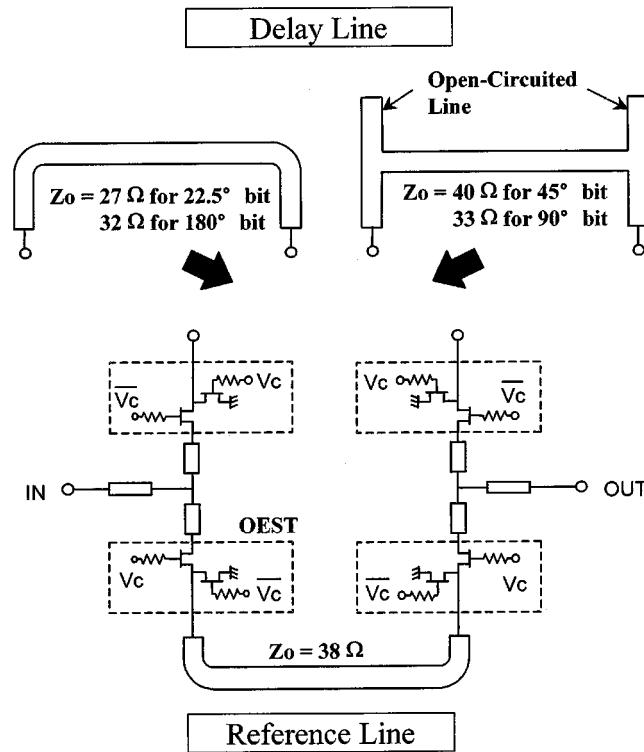

Fig. 4. Complete circuit design of each single-bit phase shifter.

the reference line design, an appropriate line is added so that  $Z$  moves from  $Z_{sw}$  along a locus (A) to the  $X$ -axis on the Smith Chart. This means that the matching condition ( $\text{Im}(Z_{ci}) = 0$ ) is satisfied. For the delay line design of the  $22.5^\circ$ -bit phase shifter, a lower impedance line is used so that  $Z$  moves along a locus (B) to the  $X$ -axis. The difference of characteristic impedance produces the phase difference between reference and delay lines, while the imaginary part of  $Z$  is equal to zero for both cases. For the delay line design of the  $180^\circ$ -bit phase shifter, the line longer than the reference line by a quarter-wave length provides a phase difference of  $90^\circ$  at the center of the line. This move  $Z$  along a locus (C) to the  $X$ -axis. The impedance response is shown in Fig. 3(b) when the delay line of the  $90^\circ$ -bit phase shifter added to the switch. In this case, the desired phase difference between the reference and delay lines cannot be produced by using conventionally fabricated microstrip lines ( $Z_0 : 25\text{--}75 \Omega$ ), and  $Z$  moves from  $Z_{sw}$  along a locus (D) to have a positive imaginary value. To move it back to the  $X$ -axis, an additional capacitive open-circuited line is incorporated in the delay line. The characteristic impedance also needs to be optimized. The design approach for the delay line of the  $45^\circ$ -bit phase shifter is the same as that of the  $90^\circ$ -bit phase shifter.

Complete circuit design of each single-bit phase shifter is shown in Fig. 4. Length and width for lines were optimized in detail involving the effects of bends, T-junctions, loss in the line and switches to obtain good return loss and desired phase shift on a circuit simulator. Characteristic impedance's of all lines are lower than  $50 \Omega$ . Return loss better than  $18 \text{ dB}$  was designed for each-bit phase shifter over a frequency range from  $32.5$  to  $35.5 \text{ GHz}$ . For the 4-bit phase shifter, the maximum phase deviation to the desired phase was designed to be  $6^\circ \text{ rms}$  for 16 states

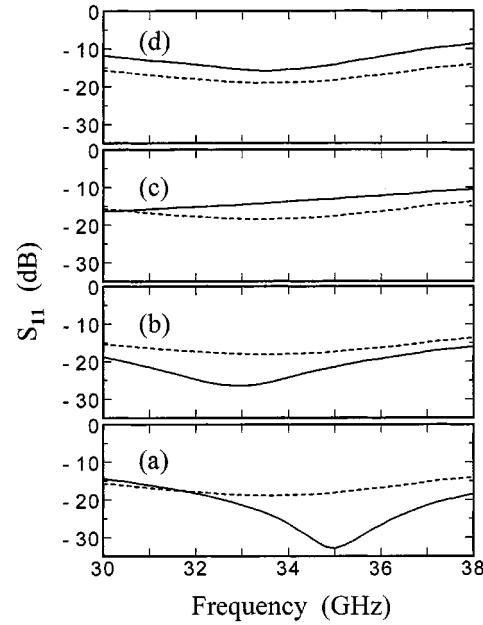

Fig. 5. Measured return loss for: (a)  $22.5^\circ$ -, (b)  $45^\circ$ -, (c)  $90^\circ$ -, and (d)  $180^\circ$ -bit phase shifters. Solid and dotted lines represent data when a signal passed through the delay and reference lines, respectively.

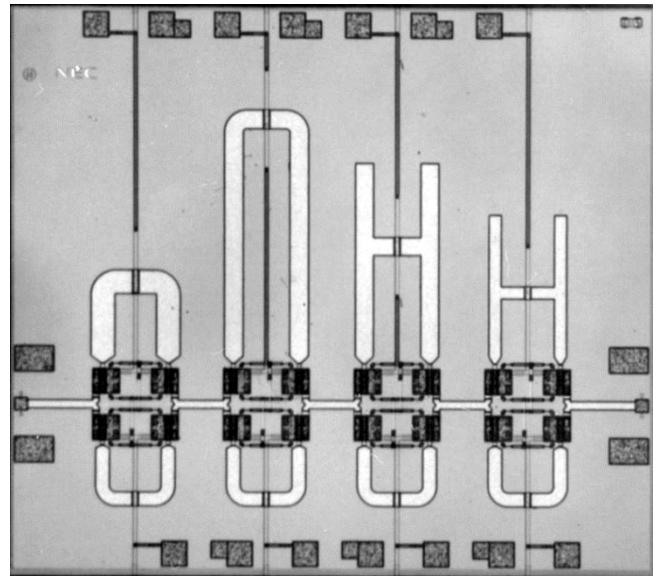

Fig. 6. Chip photograph for the fabricated 4-bit monolithic phase shifter ( $2.5 \text{ mm} \times 2.2 \text{ mm}$ ).

over the same frequency range, which is mainly determined by a linear phase-frequency relation for the delay lines. With this circuit topology, the layout is simple, which is an advantage of the switched-line configuration.

### III. FABRICATION PROCESS AND DEVICE CHARACTERISTICS

The employed monolithic-microwave integrated-circuit (MMIC) process has been developed for millimeter-wave high-power applications [7]. The heterojunction FET's (HFET's) for the switch elements consist of an InGaAs channel layer sandwiched between Si-doped AlGaAs layers. This structure leads to high current density, which is essential

(a)

(b)

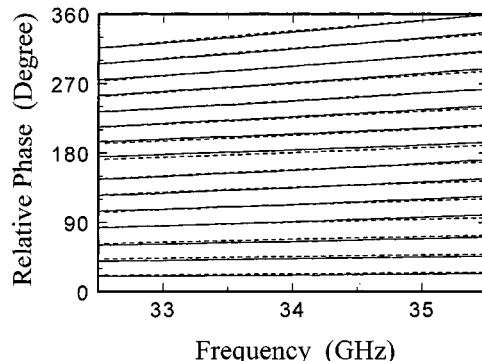

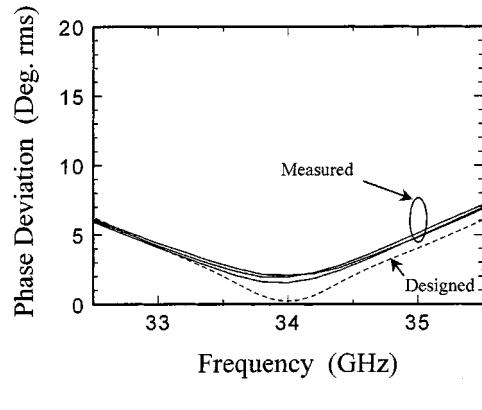

Fig. 7. Phase-shift characteristics of the phase shifter. (a) Phase delay for all 16 states. Solid lines represent measured data and dotted lines represent designed data. (b) rms phase deviations to the desired phase for three different chips.

for low insertion loss of the switch. The HJFET has a T-shaped gate with  $0.15\text{-}\mu\text{m}$  length. The device exhibited a typical transconductance of  $400\text{ mS/mm}$  and an  $f_{\text{max}}$  of  $200\text{ GHz}$  with a reverse gate–drain breakdown voltage of  $10\text{ V}$ . For the OEST switch with  $100\text{-}\mu\text{m}$ -gate-wide FET's,  $R_{\text{on}}$  and  $C_{\text{off}}$  were estimated to be  $9\text{ }\Omega$  and  $10\text{ fF}$ . Parasitic capacitance's  $C_{\text{ps}}$  and  $C_{\text{pd}}$ , as shown in Fig. 1, were also estimated to be both  $10\text{ fF}$ .

#### IV. PHASE-SHIFTER PERFORMANCE

To confirm design feasibility, return loss and phase delay were measured for each single-bit phase shifter. As shown in Fig. 5, the measured return loss was better than  $12\text{ dB}$  for each single-bit phase shifter over a frequency range from  $32.5$  to  $35.5\text{ GHz}$ . The insertion loss variation of each single-bit phase shifter was from  $3.0$  to  $3.8\text{ dB}$ , regardless of which reference or delay line was selected. At  $34\text{ GHz}$ , the phase-shift deviation to the desired value was less than  $2.5^\circ$  for each single-bit phase shifter.

A chip photograph for the fabricated 4-bit monolithic phase shifter is shown in Fig. 6. The  $22.5^\circ$ -,  $180^\circ$ -,  $90^\circ$ -, and  $45^\circ$ -bit phase shifters are connected in series. The chip size is  $2.5\text{ mm} \times 2.2\text{ mm} \times 0.04\text{ mm}$ . MMIC chips were tested using RF probes. Control voltages of  $0$  and  $-5\text{ V}$  were applied to the OEST switches. The phase-shift characteristics are shown in Fig. 7. For 16 states, the measured and designed relative phases were

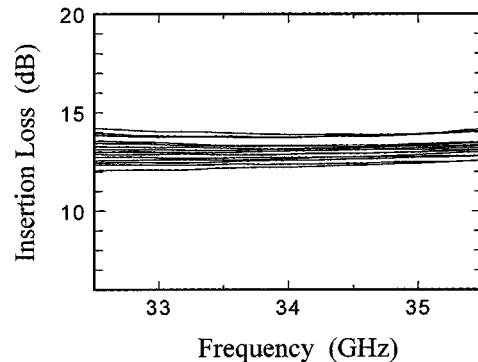

Fig. 8. Measured insertion loss of the phase shifter for all 16 states.

good agreement. The rms phase deviations to the desired phase were measured for three different chips. The phase deviations were less than  $5^\circ$  rms from  $33$  to  $35\text{ GHz}$  and  $7^\circ$  rms from  $32.5$  to  $35.5\text{ GHz}$ . At the center frequency of  $34\text{ GHz}$ , a phase deviation less than  $2.2^\circ$  rms was obtained.

The measured insertion loss is shown in Fig. 8. An insertion loss for 16 states was  $13.1 \pm 1.1\text{ dB}$  from  $34$  to  $36\text{ GHz}$ . This value is comparable to the published data ( $12.8 \pm 1.8\text{ dB}$  from  $35$  to  $37\text{ GHz}$ ) for the FET-switch-based 4-bit phase shifter [3]. The excellent flatness of insertion loss versus frequency was originated from broad-band switch characteristics. An insertion-loss variation less than  $0.65\text{-dB}$  rms was measured from  $33$  to  $35\text{ GHz}$ . Over this frequency range, the measured input and output VSWR's were better than  $1.6$  for all 16 states.

#### V. CONCLUSION

Design consideration and performance of a  $Ka$ -band monolithic phase shifter utilizing broad-band nonresonant FET switches were described in this paper. In the circuit design, characteristic impedance's for the reference and delay lines were optimized and additional open-circuited lines were introduced into delay lines of the  $45^\circ$ - and  $90^\circ$ -bit phase shifters based on the schematic design approach. The 4-bit switched-line monolithic phase shifter demonstrated an overall phase deviation less than  $5^\circ$  rms and an insertion loss variation less than  $0.65\text{-dB}$  rms from  $33$  to  $35\text{ GHz}$ . An insertion loss of  $13.1 \pm 1.1\text{ dB}$  and VSWR less than  $1.6$  were obtained for 16 states. The developed phase shifter featuring small chip size as well as excellent performance promises great applicability to  $Ka$ -band phased-array antenna systems.

#### ACKNOWLEDGMENT

The authors wish to thank S. Kainuma, A. Tanaka, E. Matsumura, Y. Hori, M. Madhian and W. Contrata for their valuable technical discussions, and E. Mizuki for her assistance. Encouragement from M. Kuzuhara, K. Honjo, I. Mito, T. Uji, and M. Ogawa is also appreciated.

#### REFERENCES

- [1] V. E. Dunn, N. E. Hodges, O. Sy, and W. Alyassini, "MMIC components for mm-wavelength active arrays," *Microwave J.*, pp. 109–116, Dec. 1989.

- [2] M. Aust, H. Wang, R. Carandang, K. Tan, C. H. Chen, T. Trinh, R. Esfandiari, and H. C. Yen, "GaAs monolithic components development for *Q*-band phased array application," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Albuquerque, NM, June 1992, pp. 703-706.

- [3] A. J. Slobodnik, Jr., R. T. Webster, and G. A. Roberts, "A monolithic GaAs 36 GHz four-bit phase shifter," *Microwave J.*, pp. 106-111, June 1993.

- [4] J. Putnam, M. Barter, K. Wood, and J. LeBlanc, "A monolithic GaAs PIN switch network for a 77 GHz automotive collision warning radar," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Denver, CO, June 1997, pp. 753-756.

- [5] H. Mizutani, M. Funabashi, and M. Kuzuhara, "DC-50 GHz small-size HJFET MMIC switch for high power applications," in *26th European Microwave Conf. Dig.*, Prague, Czech Republic, Sept. 1996, pp. 949-952.

- [6] H. Mizutani, M. Funabashi, M. Kuzuhara, and Y. Takayama, "Compact DC-60 GHz HJFET MMIC switches using ohmic electrode sharing technology," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 1597-1603, Nov. 1998.

- [7] Y. Hori, K. Onda, M. Funabashi, H. Mizutani, K. Maruhashi, A. Fujihara, K. Hosoya, T. Inoue, and M. Kuzuhara, "Manufacturable and reliable millimeter-wave HJFET MMIC technology using novel 0.15  $\mu$ m MoTiPtAu gates," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Orlando, FL, May 1995, pp. 431-434.

**Kenichi Maruhashi** (M'95) was born in Aichi, Japan, on February 11, 1967. He received the B.S. and M.S. degrees in physics from Kobe University, Kobe, Japan, in 1989 and 1991, respectively.

In 1991, he joined the NEC Corporation, Shiga, Japan, where he was involved with the modeling, design, and characterization of heterojunction FET's and development of microwave and millimeter-wave MMIC's based on their technologies. His current research interest includes developments of millimeter-wave IC's and RF front-end modules for high-speed wireless communication systems. He is currently an Assistant Manager of the Photonic and Wireless Devices Research Laboratories, System Devices and Fundamental Research, NEC Corporation, Shiga, Japan.

Mr. Maruhashi is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Hiroshi Mizutani** (M'97) received the B.S. and M.E. degrees from Kyoto University, Kyoto, Japan, in 1986 and 1988, respectively.

In 1988, he joined the NEC Corporation, Kawasaki, Japan, where he has been engaged in the development of GaAs process technology, development of GaAs power MESFET's, and research and development of millimeter-wave GaAs MMIC's. He is currently an Assistant Manager with the System ULSI Development Division, NEC Corporation, Kawasaki, Japan. His current interest includes millimeter-wave MMIC's, especially novel switch circuits for millimeter-wave applications.

Mr. Mizutani is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Keiichi Ohata** (M'86) received the B.E. and M.E. degrees in electronic engineering from Kyoto University, Kyoto, Japan, in 1970 and 1972, respectively.

In 1972, he joined the Central Research Laboratories, NEC Corporation, Kawasaki, Japan, where he was engaged in the research of ohmic contacts to GaAs, development of low-noise GaAs MESFET's, and research and development of microwave and millimeter-wave heterojunction devices. From 1991 to 1996, he was temporarily transferred to the Advanced Millimeter Wave Technologies Corporation Ltd., Shiga, Japan, where he was responsible for the research of 60-GHz-band MMIC's for short-range communication systems. He is currently a Senior Principal Researcher at the Photonic and Wireless Devices Research Laboratories, System Devices and Fundamental Research, NEC Corporation, Shiga, Japan, where he performs research and development of millimeter-wave devices for multimedia communications.

Mr. Ohata is a member of the IEEE Microwave Theory and Techniques Society, the IEEE Electron Devices Society, and the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.