# An Efficient CAD-Oriented Large-Signal MOSFET Model

Andrey V. Grebennikov, *Member, IEEE*, and Fujiang Lin, *Senior Member, IEEE*

**Abstract**—An efficient computer-aided-design-oriented large-signal microwave model for silicon MOSFETs is presented based on the well-founded small-signal equivalent circuit including self-heating effect and charge conservation condition. The proposed new single continuously differentiable empirical equations for drain current and gate capacitance are simple and quite accurate. The model parameters in the equations are constructed in such a way that they can be easily and straightforwardly extracted from measured data. Temperature effect is predicted by simply adopting the linear temperature-dependent model parameters for threshold voltage, saturation current, capacitance, and series resistances. The presented model is a good compromise between the simplicity of numerical calculations and the accuracy of final results that is desired by circuit designers in nonlinear circuit simulation.

**Index Terms**—Equivalent circuit, LDMOSFET, MOSFET RF modeling, Serenade, simulation.

## I. INTRODUCTION

PERSONAL wireless communication services have been driving intensive activities in silicon MOSFET worldwide for reliable low-cost and high-performance technology [1], [2]. For example, the LDMOS device structures have proven to be highly efficient, high gain, and linear for both high-power and low-voltage microwave and RF applications, including power amplifiers, low-noise amplifiers, mixers, and voltage-controlled oscillators [3]–[5]. In order to develop a low-cost silicon MOSFET for continued and demanded higher speed, higher frequency integrated circuits (ICs), and subsystems within shorter design time, it is necessary to have accurate device models for efficient intensive computer-aided design (CAD) simulation [6]. However, there is lack of such an efficient microwave MOSFET model. Reported popular physical models, such as the BSIM3v3 model, are too complex to be created correctly. Also, most of the models may not be accurate for RF IC simulation due to their derivative discontinuity with respect to the overall bias conditions. Moreover, microwave parasitic effects in silicon MOSFETs are not easy physically predictable. Table-based models, such as the HP Root model, are only accurate for the characterized structures and measurement conditions. An empirical modeling approach is a good compromise between physical and data-based models. It has been proven by excellent success in GaAs monolithic-microwave integrated-circuit (MMIC) development.

Manuscript received August 18, 1999.

A. V. Grebennikov is with the Institute of Microelectronics, 117685 Singapore.

F. Lin is with the Singapore Microelectronics Modeling Center, Agilent Technologies, 119958 Singapore.

Publisher Item Identifier S 0018-9480(00)08735-4.

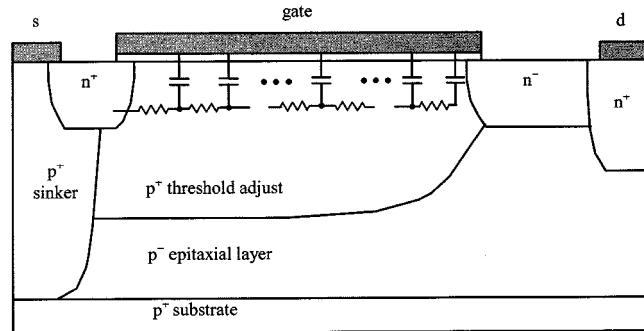

Fig. 1. Schematic representation of the MOSFET distributed channel structure.

In this paper, we report an empirical CAD nonlinear model for microwave silicon MOSFETs. Based on the well-founded small-signal MOSFET equivalent circuit, a new equation-based nonlinear model is empirically constructed from measured characteristics. Although the proposed empirical equations are simple, they describe the nonlinear behavior of the drain-current source and device intrinsic capacitances well. The realization of a single equation to cover wide operation bias conditions from subthreshold to deep inversion warrants the continuous derivatives and charge conservation. These requirements are necessary to predict the accurate third-order intermodulation distortion (IMD) in the harmonic-balanced simulation at large signal levels [7]. Moreover, the equations are constructed in such a way that the model parameter can be easily extracted in a straightforward way or small optimization with only few parameters. In the following sections, this will be described in detail.

## II. EQUIVALENT CIRCUIT

In order to accurately describe the nonlinear properties of the large devices, such as LDMOSFETs, it is first necessary to take into account the distributed nature of the device structure along both its channel length and channel width. The distributed effect along the channel length can be modeled as a bias-dependent  $RC$  distributed transmission line when the channel charging resistance should be considered, as shown in Fig. 1 [8]. The channel charging resistance  $R_{ch}$  is a result of noninstantaneous response to the changes of the gate–source voltage. In this case, under an assumption of gradual-channel approximation, the equivalent input impedance  $Z_{gs}$  seen from gate and source can be written as

$$Z_{gs} = R_{ch} \frac{\coth(\gamma L)}{\gamma L} \quad (1)$$

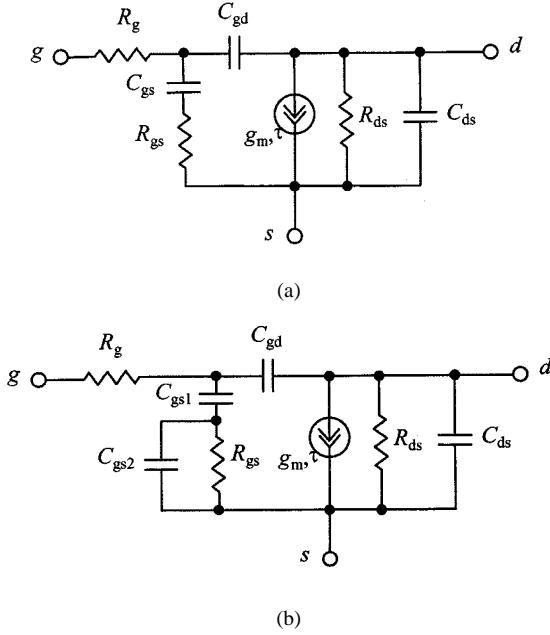

Fig. 2. Intrinsic MOSFET equivalent circuits corresponding to: (a) first- and (b) second-order channel approximation.

where  $L$  is the channel length,  $\gamma = \sqrt{j\omega R'_{\text{ch}} C'_g}$  is the propagation constant, and  $R'_{\text{ch}} = R_{\text{ch}}/L$ ,  $C'_g = C_g/L$ ,  $C_g$  is the total gate capacitance.

The first-order approximation of  $Z_{\text{gs}}$  obtained from a series expansion of (1) gives

$$Z_{\text{gs}} = R_{\text{ch}} \frac{\coth(\gamma L)}{\gamma L} \simeq \frac{R_{\text{ch}}}{\gamma L} \left( \frac{1}{\gamma L} + \frac{\gamma L}{3} \right) = \frac{R_{\text{ch}}}{3} + \frac{1}{j\omega C_g}. \quad (2)$$

From (2), it follows that the MOSFET intrinsic gate-source channel circuit can be realized by a simple series circuit with the resistance  $R_{\text{gs}} = R_{\text{ch}}/3$  and the capacitance  $C_{\text{gs}} = C_g$ . Some improvement can be achieved as a result of the second-order approximation of  $Z_{\text{gs}}$ , also derived from a series expansion of (1) as

$$\begin{aligned} Z_{\text{gs}} &= R_{\text{ch}} \frac{\coth(\gamma L)}{\gamma L} \simeq \frac{R_{\text{ch}}}{\gamma L} \left[ \frac{1}{\gamma L} + \frac{\gamma L}{3} - \frac{(\gamma L)^2}{45} \right] \\ &= \frac{R_{\text{ch}}}{3} \left( 1 - \frac{j\omega C_g R_{\text{ch}}}{15} \right) + \frac{1}{j\omega C_g} \\ &\simeq \frac{R_{\text{ch}}}{3} \left/ \left( 1 + j\omega \frac{R_{\text{ch}}}{3} \frac{C_g}{5} \right) \right. + \frac{1}{j\omega C_g}. \end{aligned} \quad (3)$$

As a result, the second-order approximation of the channel structure can be realized by a series connection of the capacitance  $C_{\text{gs}1} = C_g$  and the parallel  $RC$  circuit, which consists of the resistance  $R_{\text{gs}} = R_{\text{ch}}/3$  and the capacitance  $C_{\text{gs}2} = C_g/5$ . The intrinsic transistor equivalent circuits corresponding to: 1) first-order approximation and 2) second-order approximation are shown in Fig. 2.

For a high-power MOSFET device, whose channel width is significantly larger than channel length, it is necessary to take into consideration the distributed character of the total gate resistance  $R_t = R_{\text{sh}}W/L$  across the width  $W$  of the device,

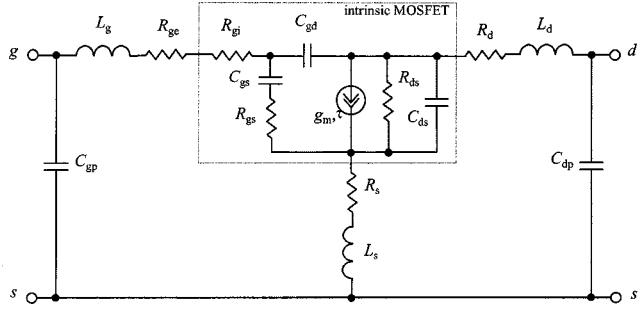

Fig. 3. Nonlinear MOSFET equivalent circuit with extrinsic linear elements.

where  $R_{\text{sh}}$  is the sheet resistance of the gate material. The silicon MOSFET can be decomposed into  $n$  devices, each with a width of  $W/n$  and a gate resistance of  $R_t/n$ . For  $n \rightarrow \infty$ , it will be viewed as an array of the small transistors distributed along the gate of the device. In a common case, it is necessary to consider a complicated two-dimensional power MOSFET distributed model because of its gate distributed character along both the channel length and channel width. However, due to the short channel size of the MOSFETs, a distributed gate effect along the channel length can be taken into account only in the frequency range close to the transition frequency  $f_T$  and higher. For the case when  $\omega R_{\text{gs}} C_{\text{gs}} \ll 1$ , the application of a transmission-line theory to analyze this distributed gate model along the channel width shows that all of the transistor  $Y$ -parameters should be modified by the term  $\tanh(\gamma W)/\gamma W$  [9]. However, a linear series expansion of this term in the form of

$$\frac{\tanh(\gamma W)}{\gamma W} = 1 - j\omega C_g \frac{R_t}{3} \simeq \frac{1}{1 + j\omega C_g \frac{R_t}{3}} \quad (4)$$

leads, in essence, only to an additional use of a series lumped gate resistance  $R_t/3$  that does not alter the structure of the transistor equivalent circuit. Consequently, the total gate resistance  $R_g$  should be divided in two series resistances as  $R_g = R_{\text{ge}} + R_{\text{gi}}$ , where  $R_{\text{ge}}$  is the extrinsic contact and ohmic gate electrode resistance and  $R_{\text{gi}} = R_t/3$  is the intrinsic voltage-dependent gate resistance due to the distributed gate structure of a power MOSFET.

In order to accurately describe the device behavior in hybrid or MMIC RF applications, the extrinsic linear elements can be added to the intrinsic nonlinear MOSFET model, as shown in Fig. 3. To evaluate the accuracy and verify the frequency limitation of a proposed small-signal model, three different power MOSFET test cells with the gate length  $L = 1.25 \mu\text{m}$  and the gatewidth  $W = 1.44 \text{ mm}$  have been measured. They are the 28-V LDMOSFET (MOSFET1), 12.5-V LDMOSFET (MOSFET3), and 28-V LDMOSFET with reduced value of  $R_g$  (MOSFET2). To extract the small-signal MOSFET equivalent-circuit parameters, on-wafer  $S$ -parameter measurements were performed for each cell in the frequency range of 50 MHz up to 10 GHz with a subsequent optimization procedure to minimize the error function in the form of

$$\varepsilon_{ij} = \frac{1}{4} \sum_{i,j=1}^2 \left( \frac{1}{N} \sum_{n=1}^N \frac{|\text{meas}S_{ijn} - \text{sim}S_{ijn}|}{\text{meas}S_{ijn}} \right) \cdot 100\% \quad (5)$$

TABLE I

RELATIVE ERRORS OF  $S$ -PARAMETERS FOR MEASURED AND EXTRACTED PARAMETERS

| Transistor | $\mathcal{E}_{11}$ , % | $\mathcal{E}_{12}$ , % | $\mathcal{E}_{21}$ , % | $\mathcal{E}_{22}$ , % |

|------------|------------------------|------------------------|------------------------|------------------------|

| MOSFET1    | 0.76                   | 0.25                   | 1.35                   | 0.73                   |

| MOSFET2    | 1.85                   | 0.81                   | 1.61                   | 1.68                   |

| MOSFET3    | 1.24                   | 2.87                   | 1.26                   | 1.91                   |

where  $\text{meas } S_{ijn}$  are the measured  $S$ -parameter data,  $\text{sim } S_{ijn}$  are the simulated ones,  $N$  is the number of frequencies, and  $i, j = 1, 2$ . The results of the relative errors of the measured and simulated  $S$ -parameters for MOSFET cells are presented in Table I, which indicate a good accuracy for a proposed MOSFET equivalent-circuit model.

Thus, in order to characterize the transistor electrical properties, it is sufficient to use the grounded-source intrinsic  $Y$ -parameters, the two-port admittance matrix of which is as follows:

$$Y = \begin{bmatrix} \frac{j\omega C_{gs}}{1+j\omega\tau_g} + j\omega C_{gd} & -j\omega C_{gd} \\ \frac{g_m \exp(-j\omega\tau)}{1+j\omega\tau_g} - j\omega C_{gd} & G_{ds} + j\omega(C_{ds} + C_{gd}) \end{bmatrix} \quad (6)$$

where  $\tau_g = R_{gs}C_{gs}$ ,  $\tau$  is the effective channel carrier transit time. As for the intrinsic gate resistance  $R_{gi}$ , under numerical calculation, it can be considered as an external gate element.

### III. MODEL DERIVATION

In many applications, it is necessary to take into consideration the MOSFET operation in the weak-inversion region when the gate-to-source voltage  $V_{gs}$  is smaller than the threshold voltage  $V_{th}$ , e.g., to improve the conversion gain of a mixer or to reduce the IMD of a class-AB power amplifier when an active device is biased at a low-current level around the onset of the strong-inversion region from the weak-inversion region. Also, there is a great influence of input capacitance  $C_{gs}$  on the IMD level when the frequency increases in the microwave region [10]. Besides, the use of nonlinear capacitance  $C_{gs}$  can improve the simulated dc power consumption [11]. The drain current in the weak-inversion region is mainly dominated by the diffusion component that increases exponentially with the gate voltage [8]. On the other hand, in the strong-inversion saturation region, when the gate-to-source voltage is greater than the threshold voltage, the drain current is proportional to the square of  $(V_{gs} - V_{th})$ . Unfortunately, in the Berkeley short-channel IGFET model (BSIM) model, which is based on the device physics of a small-geometry MOSFET, the total drain current is modeled as the linear sum of a strong inversion component and a weak inversion component [12]. Such an approach results in a very sharp transition from weak-to-strong inversion regions.

A systematic approach for the extraction of the LDMOSFET model parameters is presented in [13]. The circuit model developed to emulate the nonlinear device current-voltage characteristic consists of a SPICE Level 1 MOSFET model, JFET model, and diode model as the basic elements. Practically the same approach with only the difference of using the special drift resistor

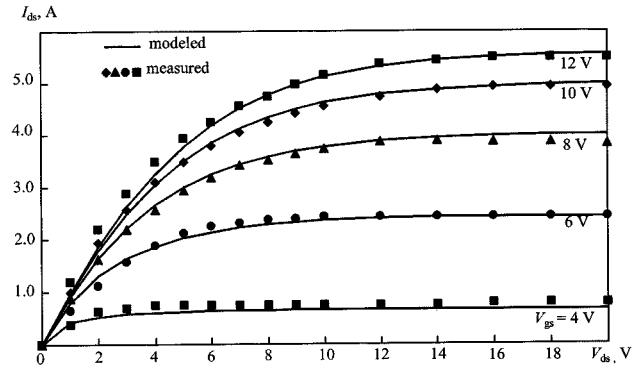

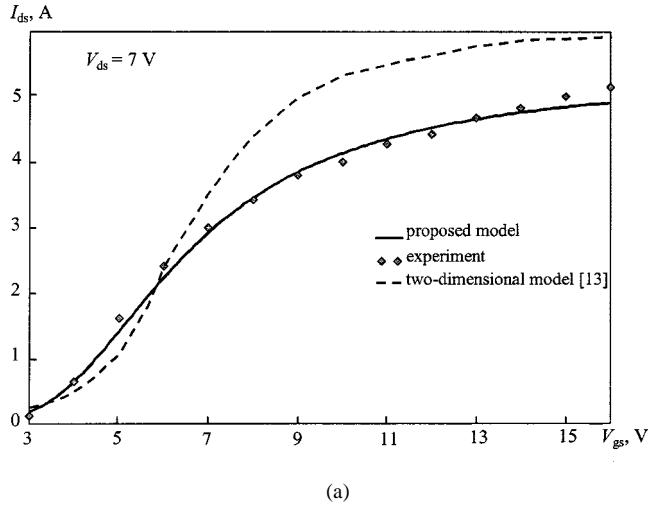

to account for the quasi-saturation effect in the drift region is presented in [14]. As a result, a systematic parameter-extraction procedure is based on the knowledge of numerous physical device parameters and measured data. However, even such an approach with careful studying and understanding of the device physics does not allow one to provide a perfect conformity between the modeled and measured data since it was originally based on a simple MOSFET static model usually used to define the nonlinear current source  $I_{ds}$  for the devices with long and wide channels. Therefore, the difference between measured and modeled curves  $I_{ds}(V_{gs}, V_{ds})$  is more than 10% for both the large and small values of the gate-source voltage  $V_{gs}$  [13].

In order to provide a continuous behavior from a weak-inversion region to a strong-inversion region for the drain current and to achieve a compromise between accurate device modeling and ease of circuit analysis, a new simple equation-based empirical MOSFET model is developed.

#### A. Drain-Current Source

To propose a new empirical nonlinear model that accurately describes the drain-source current-voltage characteristic, two preliminary analytical premises were taken into consideration. First, for a quadratic character of the MOSFET transfer dependence in the strong-inversion region, the transfer drain-current function can be written as follows:

$$I_{ds}(V_{gs}) = A \left\{ \ln [1 + \exp(B(V_{gs} - V_{th}))] \right\}^2 \quad (7)$$

where  $A$  and  $B$  are the approximation parameters. As follows from (7), the drain current is effectively proportional to the square of  $(V_{gs} - V_{th})$  when  $V_{gs}$  is larger than  $V_{th}$  and exponentially decreases with the gate voltage when  $V_{gs}$  is smaller than  $V_{th}$ . The similar approximation, which is used in the Enz-Krummenacher-Vittoz (EKV) MOST model, has been successfully applied to low-voltage and low-current analog circuit design and simulation [15]. The approximation parameters  $A$  and  $B$  are defined from the following conditions:

$$I_{ds}|_{V_{gs}=V_{th}} = I_{th} \quad \left. \frac{\partial I_{ds}}{\partial V_{gs}} \right|_{V_{gs}=V_{th}} = S_{th} \quad (8)$$

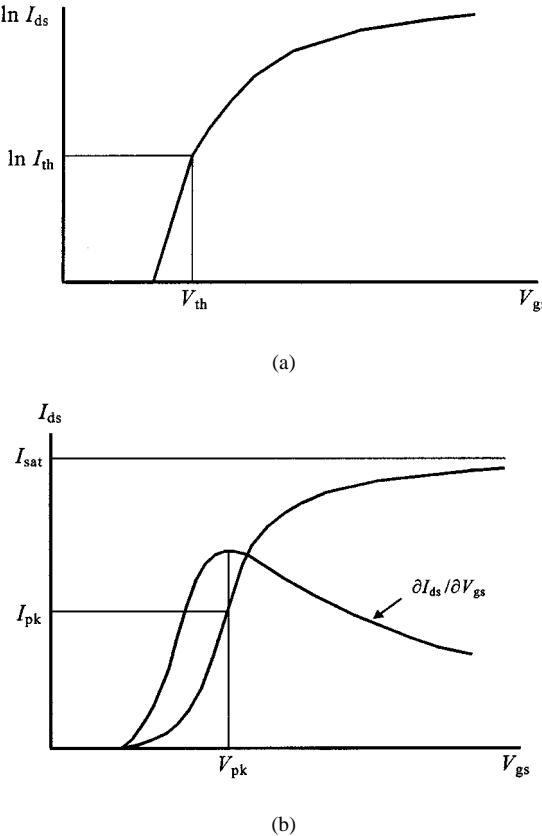

where  $I_{th}$  is the threshold drain current, as shown in Fig. 4(a), and  $S_{th}$  is a slope of the transfer current-voltage characteristic in the threshold point. Then

$$A = \frac{I_{th}}{(\ln 2)^2} \quad B = \frac{S_{th}}{I_{th}} \ln 2. \quad (9)$$

Consequently, to define the transfer characteristic it is quite enough to be limited to two physical parameters  $I_{th}$  and  $S_{th}$ , which are easily defined from the device measurements.

To link the linear and saturation regions by continuous analytical dependence, the following function to represent the current-voltage characteristic of the HEMT devices was used [7]:

$$I_{ds}(V_{gs}, V_{ds}) = (I_{\max}^{-1} + I_{ds0}^{-1})^{-1} \quad (10)$$

where  $I_{ds0}$  is an exponential function of  $V_{gs}$  and  $V_{ds}$ , and  $I_{\max}$  is maximum channel current expressed by

$$I_{\max}(V_{ds}) = I_{pk}(1 + \lambda V_{ds}) \tanh(\alpha V_{ds}). \quad (11)$$

$I_{pk}$  is the drain current, which is corresponded to maximum slope of the  $I_{ds}$ - $V_{gs}$  curve, as shown in Fig. 4(b). Parameter  $\alpha$  is

Fig. 4. Drain current  $I_{ds}$  versus gate-source voltage  $V_{gs}$ .

the saturation voltage parameter, which has an effect on a slope of the  $I_{ds}$ - $V_{ds}$  curves in the linear region, whereas parameter  $\lambda$  determines a slope of the same curves in the saturation region. The use of a hyperbolic tangent function has been successfully applied to approximate with good accuracy the entire  $I_{ds}$ - $V_{ds}$  curves of the JFET, MESFET, and HEMT drain-current sources [16]–[18].

Then, in view of the quite sloping character of  $I_{ds}$ - $V_{ds}$  curves, and by taking into account two analytic preliminary premises presented by (7) and (10), the entire current-voltage characteristic of a MOSFET can be described as follows:

$$I_{ds}(V_{gs}, V_{ds}) = I_o \left[ 1 + \left( \frac{I_o}{I_{\max}} \right)^n \right]^{1/n} \quad (12)$$

where

$$I_o = \frac{I_{th}}{(\ln 2)^2 (1 - \beta V_{gs})} \cdot \left\{ \ln \left[ 1 + \exp \left( \frac{S_{th} \ln 2}{I_{th}} (V_{gs} - V_{th}) \right) \right] \right\}^2$$

$$I_{\max} = I_{sat} (1 + \lambda V_{ds}) \tanh(\alpha V_{ds})$$

$I_{sat}$  is the saturated drain current, as shown in Fig. 4(b),  $V_{th} = V_{th0} - \sigma V_{ds}$ ,  $\beta$  is the fitting parameter, which determines a slope of  $I_{ds}$ - $V_{gs}$  curves under the large values of  $V_{gs}$ , and  $\sigma$  is the parameter, which empirically expresses the dependence of the threshold voltage on  $V_{ds}$ . Better accuracy can be achieved by using  $I_{sat}$  in the expression for  $I_{\max}$  in (11) instead of  $I_{pk}$ .

### B. Capacitances

Attempting to calculate the gate-source capacitance  $C_{gs}$  or the gate-drain capacitance  $C_{gd}$  from the charges corresponding only to the accurate strong-inversion model results in a very complicated expression [8]. Therefore, in some cases of MOSFET modeling, the capacitances  $C_{gs}$  and  $C_{gd}$  can be modeled as the fixed capacitances measured at the quiescent bias voltage and p-n junction diode capacitance model can be applied to the capacitance  $C_{ds}$  [13]. In [14], only the drain-source capacitance  $C_{ds}$  and gate-drain capacitance  $C_{gd}$  are considered as the bias-dependent junction capacitances. With an increase in the bias voltage, a depletion region is formed under the oxide in the lightly doped drain region. Therefore, the capacitance  $C_{gd}$  can be considered as a junction capacitance, which strongly depends on the drain-source bias voltage  $V_{ds}$ . According to the accurate charge model calculations in [8],  $C_{gd}$  has a strong dependence on  $V_{gs}$  only in the moderate-inversion region when  $V_{gs} - V_{th} < 1$  V. For low-voltage MOSFET devices, the dependence of  $C_{gd}(V_{gs}, V_{ds})$  can be quite accurately approximated by trigonometric hyperbolic functions [19], [20]. However, for high-voltage LDMOSFET devices, since the dependence of  $C_{gd}$  on  $V_{gs}$  is quite small, it seems sufficient to be limited to the dependence of  $V_{ds}$  only. As to the capacitance  $C_{ds}$ , it is varied due to the change in the depletion region, which is mainly determined by the value of  $V_{ds}$ .

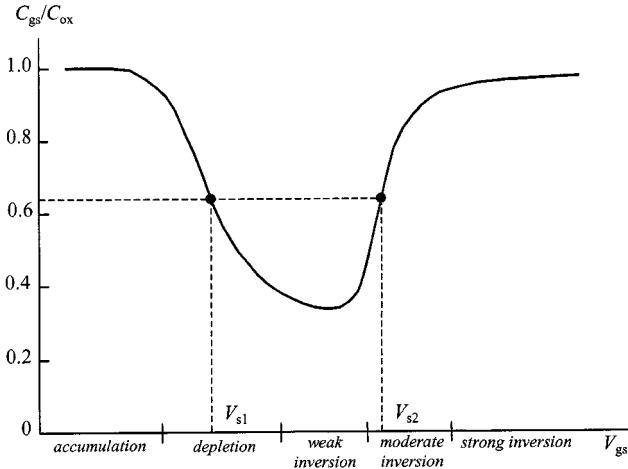

To describe the behavior of the total gate-source capacitance  $C_{gs}$ , it is necessary to separately consider an appropriate behavior of the intrinsic gate-source capacitance  $C_{gsi}$ , including both the gate-source and source-substrate charge fluctuations, and the gate-substrate capacitance  $C_{gbi}$ , the gate-source voltage dependence of which is essentially different [8]. The intrinsic gate-substrate capacitance  $C_{gbi}$  is constant in the accumulation region where it is equal to the total intrinsic oxide capacitance  $C_{ox}$ , slightly decreases in the weak-inversion region, significantly reduces in the moderate-inversion region, and becomes practically constant in the strong-inversion or saturation regions. On the contrary, the intrinsic gate-source capacitance  $C_{gsi}$  rapidly grows in the moderate inversion region and becomes equal to  $2C_{ox}/3$  in the saturation region. The dependence of the total gate-source capacitance  $C_{gs}$  as a sum of its components  $C_{gsi}$  and  $C_{gbi}$  on  $V_{gs}$  is presented in Fig. 5.

In this case, it is convenient to use a hyperbolic tangent function for each of two parts of the dependence  $C_{gs}(V_{gs})$  where the gate-source capacitance as well as the MOS junction capacitance can be approximated by the following function:

$$C_{gs} = C_{gs\min} + C_s \left\{ 1 + \tanh \left[ \frac{S}{C_s} (V_{gs} - V_s) \right] \right\} \quad (13)$$

where  $C_s = (C_{gs\max} - C_{gs\min})/2$ ,  $C_{gs\max}$  is the maximum gate-source capacitance,  $C_{gs\min}$  is the minimum gate-source capacitance, and  $S = (S_1, S_2)$  is the slope of  $C_{gs}(V_{gs})$  at each bend point  $V_{gs} = V_s = (V_{s1}, V_{s2})$ , as shown in Fig. 5

$$S_1 = \left. \frac{\partial C_{gs}}{\partial V_{gs}} \right|_{V_{gs}=V_{s1}} \quad S_2 = \left. \frac{\partial C_{gs}}{\partial V_{gs}} \right|_{V_{gs}=V_{s2}}.$$

Fig. 5. Gate-source capacitance  $C_{gs}$  versus gate-source voltage  $V_{gs}$ .

Then, the total gate-source capacitance  $C_{gs}$  as a function of  $V_{gs}$  can be described by

$$C_{gs} = C_{gs\max} - C_{gso} \left\{ 1 + \tanh \left[ \frac{S_1}{C_s} (V_{gs} - V_{s1}) \right] \right\} \times \left\{ 1 + \tanh \left[ \frac{S_2}{C_s} (V_{gs} - V_{s2}) \right] \right\} \quad (14)$$

where  $C_{gs\max} = C_{ox}$ ,  $C_{gso}$  is the model fitting parameter.

On the other hand, for high-voltage LDMOSFET devices, the dependencies of gate-drain capacitance  $C_{gd}$  and drain-source capacitance  $C_{ds}$  on  $V_{ds}$  can be accurately evaluated by means of the junction diode capacitance model as follows:

$$C_{gd(ds)} = C_{gdo(ds)} \left( \frac{\varphi + E_{ds}}{\varphi + V_{ds}} \right)^m \quad (15)$$

where  $m$  ( $m_1$  for  $C_{gd}$  or  $m_2$  for  $C_{ds}$ ) is the junction sensitivity,  $\varphi$  is the contact potential, a value of which depends on a doping profile ( $m = 1/3$  for the linearly graded junction,  $m = 1/2$  for the abrupt junction,  $m > 1/2$  for the hyperabrupt junction), and  $C_{gdo}$  and  $C_{ds0}$  are the junction capacitances when  $V_{ds} = E_{ds}$ . For practical junction profiles, which are neither exactly abrupt nor exactly linearly graded, one often chooses the parameters  $m$  and  $\varphi$  so as to obtain the best matching between the theoretical model and measurements.

### C. Charge Conservation

In order to correctly describe both small- and large-signal device models, it is necessary to satisfy a charge conservation condition. For a three-terminal MOSFET device, the matrix equation for a small-signal charging circuit in the frequency-domain representation can be given by

$$\begin{bmatrix} I_g \\ I_d \\ I_s \end{bmatrix} = j\omega \begin{bmatrix} C_{gg} & -C_{gd} & -C_{gs} \\ -C_{dg} & C_{dd} & -C_{ds} \\ -C_{sg} & -C_{sd} & C_{ss} \end{bmatrix} \cdot \begin{bmatrix} V_g \\ V_d \\ V_s \end{bmatrix} \quad (16)$$

where  $I_g$ ,  $I_d$ , and  $I_s$  are the terminal current amplitudes,  $V_g$ ,  $V_d$ , and  $V_s$  are the terminal voltage amplitudes, and the capacitance between any two device terminals ( $k, l$ ) is described as  $C_{kl} = \partial Q_k / \partial V_l$  [8]. To transform a three-terminal device into a two-port network with a common source terminal, the current and voltage terminal conditions of  $I_g = I_{gs}$ ,  $I_d = I_{ds}$ ,

Fig. 6. Measured and modeled  $I_{ds}$ - $V_{ds}$  curves of a 28-V LDMOSFET.

$I_s = -(I_{gs} + I_{ds})$ ,  $V_g - V_s = V_{gs}$ , and  $V_d - V_s = V_{ds}$  should be taken into account. Besides, for three-terminal devices, the following relations between terminal capacitances are performed:

$$\begin{aligned} C_{gg} &= C_{gd} + C_{gs} = C_{dg} + C_{sg} \\ C_{dd} &= C_{dg} + C_{ds} = C_{gd} + C_{sd} \\ C_{ss} &= C_{sg} + C_{sd} = C_{gs} + C_{ds}. \end{aligned} \quad (17)$$

Then, the admittance  $Y_c$ -matrix for such a capacitive two-port network can be easily written as

$$Y_c = \begin{bmatrix} j\omega(C_{gs} + C_{gd}) & -j\omega C_{gd} \\ -j\omega(C_{gd} + C_m) & j\omega(C_{ds} + C_m + C_{gd}) \end{bmatrix} \quad (18)$$

where  $C_m = C_{dg} - C_{gd}$  is the transcapacitance [8].

If it is taken into account that, for power MOSFET devices, the transcapacitance  $C_m$  is substantially less than  $C_{gs}$ , it can be translated to an additional delay time  $\tau_c$  in a frequency range up to  $f_T$  by combining with the transconductance  $g_m$  according to

$$\begin{aligned} g_m - j\omega C_m &= g_m \sqrt{1 + \left( \frac{\omega}{\omega_T} \frac{C_m}{C_{gs}} \right)^2} \\ &\times \exp \left[ -j \tan^{-1} \left( \frac{\omega}{\omega_T} \frac{C_m}{C_{gs}} \right) \right] \\ &\cong g_m \exp(-j\omega\tau_c) \end{aligned} \quad (19)$$

where  $\tau_c = C_m / \omega_T C_{gs}$ . As a result, to satisfy a charge conservation condition, the total delay time  $\tau$  presented in the MOSFET equivalent circuit in Fig. 3 should contain both delay time due to the ideal transit time and delay time due to the transcapacitance. Also, the transcapacitance  $C_m$  can be easily added to the drain-source capacitance  $C_{ds}$  under a parameter-extraction procedure.

### D. Gate-Source Resistance

The gate-source resistance  $R_{gs}$ , which is determined by the effect of the channel inertia in responding to rapid changes of the time varying gate-source voltage, varies in such a manner that the charging time  $\tau_g$  remains approximately constant [21]. Thus, the increase of  $R_{gs}$  in the velocity saturation region when the channel conductivity decreases is partially compensated by the decrease of  $C_{gs}$  due to nonuniform channel charge distribution [22]. The effect of  $R_{gs}$  becomes significant at higher frequencies close to the transition frequency  $f_T$  of the MOSFET and cannot practically be taken into consideration for the RF

TABLE II

SIMULATED  $I$ - $V$  MODEL PARAMETERS OF A HIGH-POWER LDMOSFET

| Parameters | $\alpha, 1/V$ | $\beta, 1/V$ | $\lambda, 1/V$ | $V_{th}, V$ | $I_{th}, A$ | $S_{th}, A/V$ | $I_{sat}, A$ | $n$ | $\sigma$ |

|------------|---------------|--------------|----------------|-------------|-------------|---------------|--------------|-----|----------|

| Values     | 0.15          | 0            | 0.0005         | 2.7         | 0.115       | 0.2           | 6.8          | 1.0 | 0        |

(a)

(b)

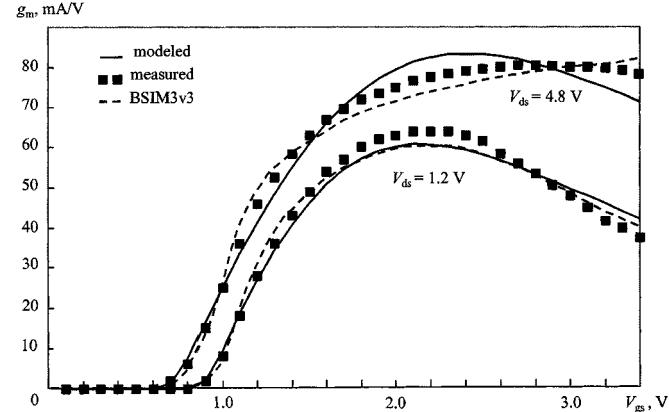

Fig. 7. Measured and modeled: (a)  $I_{ds}$ - $V_{gs}$  curves and (b)  $g_m(V_{gs})$  dependencies of a high-power LDMOSFET.

circuits operating below 2 GHz, which covers most of the commercial wireless applications [19], [23]. For example, for the MOSFET with the depletion region doping concentration value  $N_A = 1700 \mu\text{m}^{-3}$ , the phase of the small-signal transconductance  $g_m$  near  $f_T$  reaches the value of only  $-15^\circ$  [8].

#### E. Temperature Dependence

Silicon MOSFET devices are very sensitive to the operation temperature  $T$  and their characteristics are strongly temperature dependent [8]. The main parameters responsible for this are the effective carrier mobility  $\mu$  and threshold voltage  $V_{th}$ . The effect of these parameters on the transistor characteristics is such that a temperature increase leads to the increase of the drain current through  $V_{th}(T)$  and to the decrease of it through  $\mu(T)$ . Increasing temperature decreases the slope of the  $I_{ds}$ - $V_{gs}$

Fig. 8. Measured and modeled  $I_{ds}$ - $V_{ds}$  curves of a low-voltage MOSFET.

Fig. 9. Measured and modeled  $g_m(V_{gs})$  dependencies of a low-voltage MOSFET.

curves, and it can be found at a certain value of  $V_{gs}$ , at which the drain current becomes practically temperature independent over a large temperature range. The change in the value of  $V_{th}$  with temperature in a wide range from  $-50^\circ\text{C}$  up to  $200^\circ\text{C}$  represents a nonlinear function, which is slowly decreased with temperature [13], and can be approximated by the trinomial

$$V_{th}(T) = V_{th}(T_{\text{nom}}) + V_{T1}\Delta t + V_{T2}\Delta t^2 \quad (20)$$

where  $\Delta t = T - T_{\text{nom}}$ ,  $T_{\text{nom}} = 27^\circ\text{C}$  (300 K), and  $V_{T1}$  and  $V_{T2}$  are the linear and quadratic temperature coefficients for threshold voltage.

The change the value of  $\mu$  with temperature can be taken into account by introducing the appropriate temperature change of  $I_{sat}$  in (12). Thus, as the temperature change of  $I_{sat}$  represents

TABLE III

SIMULATED  $I$ - $V$  MODEL PARAMETERS OF A LOW-VOLTAGE MOSFET

| Parameters | $\alpha$ , 1/V | $\beta$ , 1/V | $\lambda$ , 1/V | $V_{th}$ , V | $I_{th}$ , mA | $S_{th}$ , mA/V | $I_{sat}$ , A | $n$  | $\sigma$ |

|------------|----------------|---------------|-----------------|--------------|---------------|-----------------|---------------|------|----------|

| Values     | 0.58           | 0.17          | 0               | 0.9          | 0.029         | 10.5            | 0.31          | 0.78 | 0.05     |

an almost straight line [13], which is decreased with temperature, the temperature dependence of  $I_{sat}(T)$  can be approximated by the linear function

$$I_{sat}(T) = I_{sat}(T_{nom}) + I_T \Delta t \quad (21)$$

where  $I_T$  is the linear temperature coefficient for saturation current.

The temperature dependencies of the MOSFET capacitances and series resistances can be described by the following linear equations [12], [24]:

$$C(T) = C(T_{nom}) + C_T \Delta t \quad (22)$$

$$R(T) = R(T_{nom}) + R_T \Delta t \quad (23)$$

where  $C = (C_{gs}, C_{ds}, C_{gd})$ ,  $R = (R_g, R_s, R_d)$ ,  $R_T$ , and  $C_T$  are the linear temperature coefficients for the capacitances and resistances, respectively.

#### F. Self-Heating

In order to correctly describe the behavior of the power MOSFET devices at all biasing conditions, it is necessary to take into account the self-heating effect. For example, at a highly dissipated power region, it leads to the negative output differential resistance due to the reduction of  $I_{ds}$  at high values of  $V_{gs}$ . The effect of the negative conductance at high biasing can be taken into account if the nonlinear  $I$ - $V$  model is rewritten in the following form:

$$I_{ds}(T, p_T) = \frac{I_{ds}(T)}{1 + p_T V_d I_{ds}(T)} \quad (24)$$

where the drain-current source  $I_{ds}(T)$  is presented by (12),  $V_d = V_{ds}/\sqrt{1 + (\omega\tau_{th})^2}$ ,  $p_T$  is self-heating temperature coefficient,  $V_{ds}$  is the drain-source supply voltage,  $\tau_{th} = R_{th}C_{th}$  is the thermal time constant,  $R_{th}$  is the thermal resistance, and  $C_{th}$  is the thermal capacitance. A thermal equivalent circuit can be added to the large-signal LDMOSFET model, as is shown in [25]. The thermal resistance  $R_{th}$  can be extracted from the temperature measurement of the dc characteristics. Since the slope of the dc measured  $I_{ds}$ - $V_{ds}$  curves changes its sign from positive to negative, the temperature coefficient  $p_T$  can be evaluated using the following condition:

$$\frac{dI_{ds}(T, p_T)}{dV_{ds}} = 0. \quad (25)$$

As a result,

$$p_T = \frac{1}{I_{ds}^2(T)} \frac{dI_{ds}(T)}{dV_{ds}} \quad (26)$$

where  $I_{ds}$ - $V_{ds}$  curves are defined by pulsed measurement at ambient temperature  $T$  and a value of  $I_{ds}(T)$  is fixed the same as for a zero slope of  $I_{ds}(T, p_T)$ .

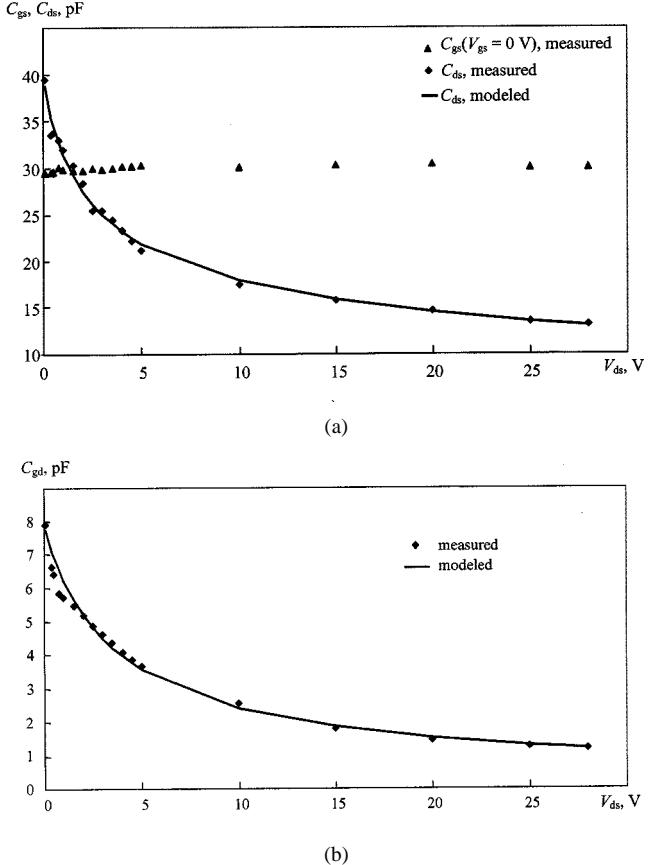

Fig. 10. Measured and modeled: (a)  $C_{gs}(V_{ds})$ ,  $C_{ds}(V_{ds})$  and (b)  $C_{gd}(V_{ds})$  dependencies of a 28-V LDMOSFET.

TABLE IV

SIMULATED  $C$ - $V$  JUNCTION MODEL PARAMETERS

| Capacitance | $C_{gd(ds)0}$ , pF | $m$  | $\varphi$ , V |

|-------------|--------------------|------|---------------|

| $C_{gd}$    | 7.88               | 0.8  | 2.94          |

| $C_{ds}$    | 39.42              | 0.33 | 1.0           |

The thermal time constant  $\tau_{th}$  can be extracted by comparing pulsed  $I_{ds}$ - $V_{ds}$  curves calculated under a different pulselength and duty factors. A plot of  $I_{ds}$  as a function of pulselength under the fixed gate-source and drain-source biasing voltages gives an appropriate value of  $\tau_{th}$ .

#### IV. MODEL SMALL-SIGNAL VERIFICATION

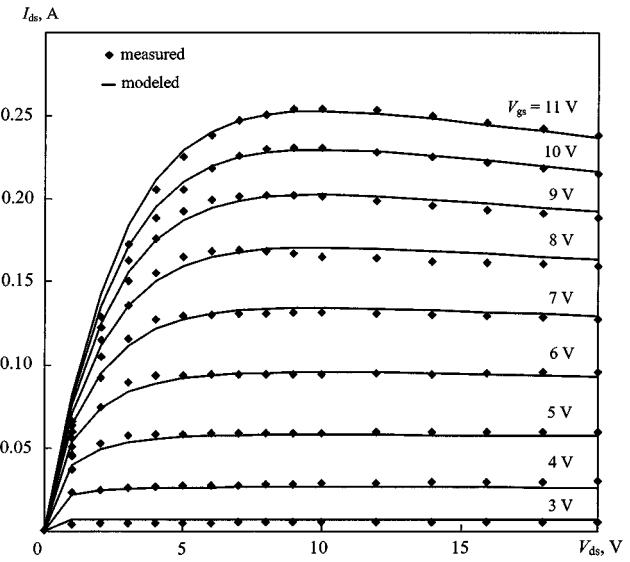

In order to verify the new empirical  $I$ - $V$  model, a 28-V high-power LDMOSFET with gatewidth of  $W = 4$  cm and gate length of  $L = 1.1 \mu\text{m}$  type LP801 from Polyfet RF devices was used. In Fig. 6, the theoretical and experimental (pulsed measurement)  $I_{ds}$ - $V_{ds}$  curves are presented. The

(a)

(b)

Fig. 11. Measured: (a)  $C_{gs}(V_{gs})$ ,  $C_{ds}(V_{gs})$ , and (b)  $C_{gd}(V_{gs})$  dependencies of a 12.5-V LDMOSFET cell.

Fig. 12. Measured and modeled gate-source voltage dependencies of  $C_{gs}$  and  $R_{gs}$ .

resulting current root-mean-square error of a family of the model  $I_{ds}$ - $V_{ds}$  curves is 0.5%. The values of simulated model parameters are indicated in Table II. As follows from Table II, the  $I_{ds}$ - $V_{ds}$  approximation is sufficiently simple and accurate in the case of a high-power LDMOSFET and requires only six fitting parameters, of which four of them are directly determined by the experimental curves.

Substantially better fitting for  $I_{ds}$ - $V_{gs}$  curve and  $g_m(V_{gs})$  dependence in comparison with the results obtained by extensive two-dimensional simulations [13] is realized (Fig. 7). The deviation of the average difference error of the model  $I_{ds}$ - $V_{gs}$  curve

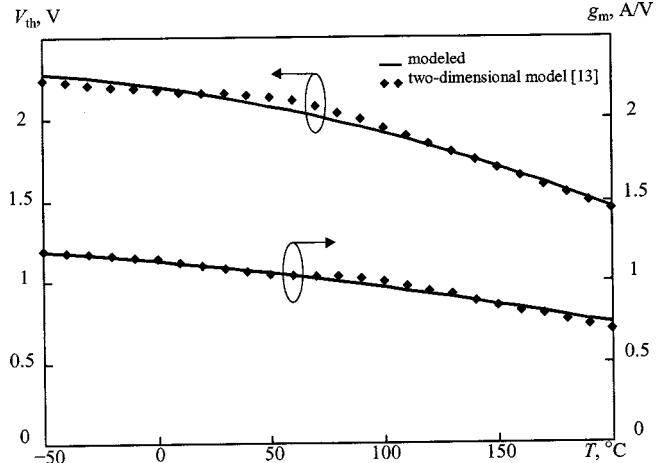

Fig. 13. Modeled temperature dependencies of  $V_{th}$  and  $g_m$ .

Fig. 14. Measured and modeled  $I_{ds}$ - $V_{ds}$  curves of a 12.5-V LDMOSFET cell.

from the experimental one is 4.4%. It can be seen that a proposed empirical model allows one to describe smoothly and sufficiently accurately the behavior of both  $I_{ds}$  and  $g_m$  as a function of  $V_{gs}$  in a weak-inversion region, as well as in the strong-inversion region of the LDMOSFET operation.

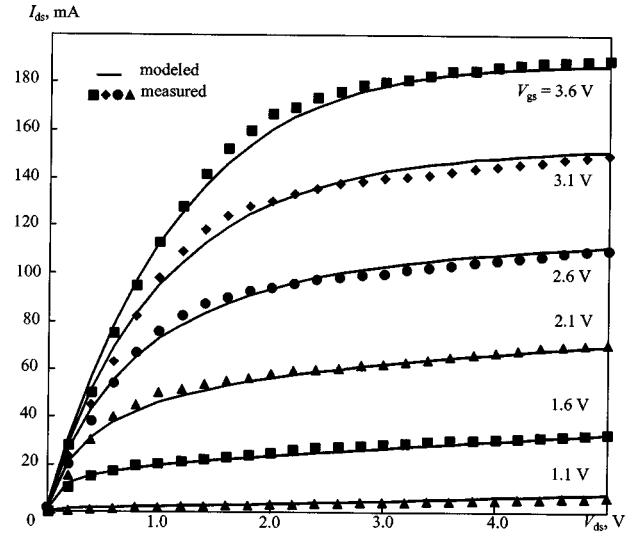

To verify an applicability of the proposed model to low-voltage MOSFET devices, the appropriate low-voltage RF power MOSFET with the gatewidth of  $W = 2$  mm was chosen [23]. In Fig. 8, the modeled and experimental  $I_{ds}$ - $V_{ds}$  curves are presented. In this case, to improve the sensitivity of drain current  $I_{ds}$  under large values of  $V_{gs}$ , the term  $(1 - \beta V_{gs})$  was introduced to the approximation function (12). The resulting root-mean-square error of a family of the  $I_{ds}$ - $V_{ds}$  curves is 0.42%. The values of  $I_{ds}$ - $V_{ds}$  model parameters are presented in Table III. The model  $I_{ds}$ - $V_{gs}$  curves were compared with the same characteristics calculated by means of the BSIM3v3 model developed for modeling of deep submicrometer device [23]. The results presented in Fig. 9 show a good agreement

TABLE V

SIMULATED  $C_{gs}$ - $V_{gs}$  MODEL PARAMETERS

| Capacitance | $C_{gs0}$ , pF | $S_1$ , pF/V | $S_2$ , pF/V | $V_{s1}$ , V | $V_{s2}$ , V | $C_s$ , pF | $C_{gsmax}$ , pF |

|-------------|----------------|--------------|--------------|--------------|--------------|------------|------------------|

| $C_{gs}$    | 9.85           | -0.8         | 1.2          | -2.1         | -0.84        | 0.94       | 5.83             |

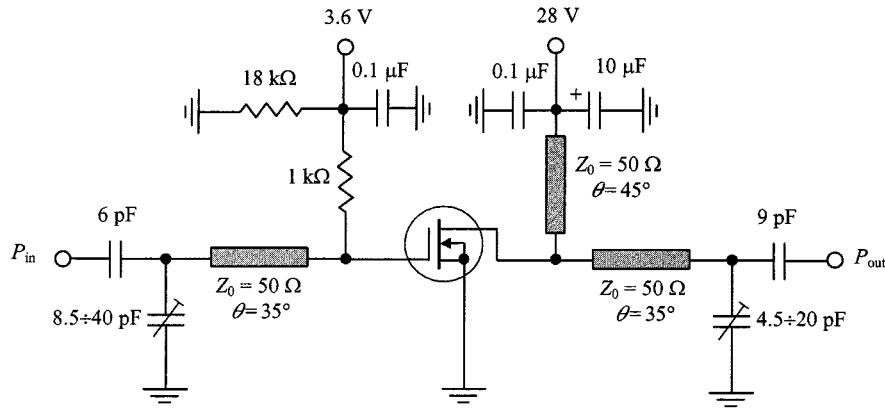

Fig. 15. Equivalent circuit of a 500-MHz 20-W LDMOSFET amplifier.

with the experimental curves and practically the same as in the case of the BSIM3v3 approximation.

The results of the approximation of  $C_{ds}$  and  $C_{gd}$  as the junction capacitances for LP801 device are given in Fig. 10(a) and (b), respectively. The fitting parameters of the approximation  $C_{gd}(V_{ds})$  and  $C_{ds}(V_{ds})$  curves are presented in Table IV. The resulting averaged differential deviation of model values from the measured ones for the gate-drain capacitance and drain-source capacitance is less than 5%.

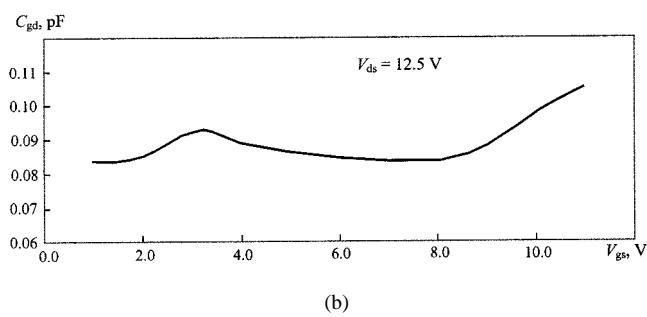

In Fig. 11(a) and (b), the measured  $C_{gs}(V_{gs})$ ,  $C_{ds}(V_{gs})$  and  $C_{gd}(V_{gs})$  curves for a 12.5-V LDMOSFET cell with a gate geometry of  $L = 1.25 \mu\text{m}$  and  $W = 1.44 \text{ mm}$  are presented, respectively, which indicate practical independence of  $C_{gd}$  and  $C_{ds}$  on  $V_{gs}$ . A linear increase of all capacitances at high values of gate bias is provided with the increase of the dissipation power under dc measurement. The dependence  $C_{gs}(V_{gs})$  has a predictable minimum near threshold voltage  $V_{th} = 2.3 \text{ V}$  and can be readily approximated by hyperbolic tangent function. The behavior of  $C_{gd}$  as a function of  $V_{gs}$  with a small increase near  $V_{th}$  is typical for high-power silicon LDMOSFET devices [25].

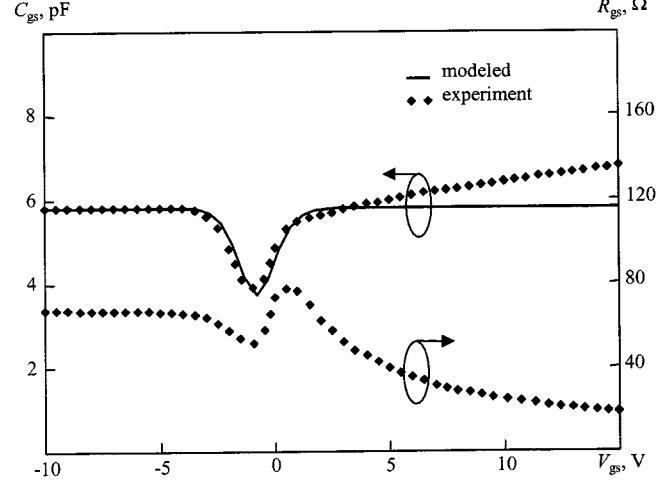

Fig. 12 shows the measured and modeled gate-source voltage dependencies of  $C_{gs}(V_{gs})$  and  $R_{gs}(V_{gs})$  for a 28-V MOSFET with a horizontal channel of  $L = 5 \mu\text{m}$ . The fitting parameters of the approximation  $C_{gs}(V_{gs})$  curve are given in Table V. Some growth of the experimental  $C_{gs}(V_{gs})$  dependence at high values of  $V_{gs}$  is also the result of high power dissipation under dc measurement. As follows from Fig. 12, the gate-source capacitance  $C_{gs}$  increases with the increase of gate-source voltage  $V_{gs}$  in the strong-inversion region, whereas channel resistance  $R_{gs}$  decreases at the same changes of  $V_{gs}$  so that the charging time  $\tau_g$  insignificantly reduces and can be approximated by a constant.

In Fig. 13, the modeled temperature dependencies of  $V_{th}(T)$  and  $g_m(T)$  for an LP801 device are presented. The results obtained by using the simple approximations (20) and (21) with

the values of  $V_{T1} = (2 \text{ mV}/\text{°C}$ ,  $V_{T2} = -8.55 \mu\text{V}/\text{°C}$ )<sup>2</sup>, and  $I_T = -4.5 \text{ mA}/\text{°C}$  show a good prediction of the  $I$ - $V$  curves in a wide temperature range.

Fig. 14 shows a comparison between the measured (dc measurement) and modeled  $I_{ds}$ - $V_{ds}$  curves for a 12.5-V LDMOSFET cell with gate geometry of  $L = 1.25 \mu\text{m}$  and  $W = 1.44 \text{ mm}$ . As follows from Fig. 14, the effect of self-heating is described quite accurately by (23) for the following model parameters:  $p_T = 0.035 \text{ 1/AV}$ ,  $\alpha = 0.2 \text{ 1/V}$ ,  $\beta = \sigma = 0$ ,  $S_{th} = 37 \text{ mA/V}$ ,  $I_{th} = 1.5 \text{ mA}$ ,  $V_{th} = 2.25 \text{ V}$ ,  $I_{sat} = 0.48 \text{ A}$ ,  $n = 1$ , and  $\lambda = 0.0005 \text{ 1/V}$ .

## V. LARGE-SIGNAL APPLICATION

Using the Ansoft CAD simulator Serenade 8.5, linear circuit analysis and amplifier nonlinear simulation were performed for the LDMOSFET device with gate geometry of  $L = 1.25 \mu\text{m}$  and  $W = 4 \text{ cm}$  at operating frequency of 500 MHz. Linear and nonlinear device model parameters were extracted from on-wafer measurements. The parameters of the matching circuit elements were chosen according to the results of the CAD simulation for the high-efficiency operating mode of the power amplifier. The experimental test structure of a single-stage 20-W LDMOSFET power amplifier is shown in Fig. 15. Two T-section transformers with series microstrip lines and parallel variable capacitors have been used as the input and output matching circuits. The matching circuits were fabricated on epoxy glass copper-clad laminate substrates and the characteristic impedances of all microstrip lines are equal to  $50 \Omega$ . In order to avoid low-frequency parasitic oscillations, the electrolytic capacitor of  $10 \mu\text{F}$  was connected in parallel to the drain supply.

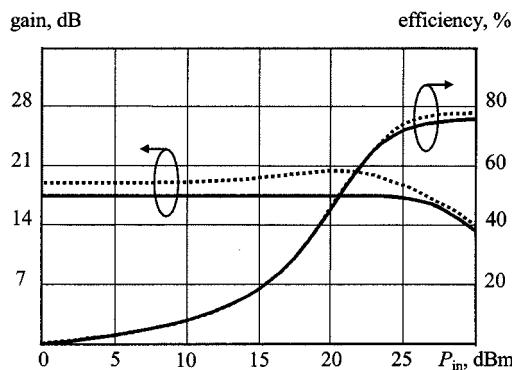

The measured (solid lines) and simulated (dotted lines) characteristics of the output power and power gain as a function of the input power are presented in Fig. 16. Maximum level of the

Fig. 16. Simulation (dotted line) and experimental (solid line) results of a 20-W LDMOSFET amplifier.

output power of 20 W with the drain efficiency of 76% and dc collector current of 0.94 A has been achieved. The difference between measured and modeled values of power-aided efficiency is practically negligible. The deviation of measured from simulated values of power gain of about 2–3 dB can be explained by sufficient gain sensitivity to the gate resistance, the exact value of which is difficult to calculate for the high-power device taking into account the distributed nature of the wide gate structure.

## VI. CONCLUSIONS

In this paper, a new simple nonlinear model has been developed on the basis of the well-founded small-signal MOSFET equivalent circuit. The proposed model is based on new simple empirical equations, which completely describe the nonlinear behavior of the drain–current source and device intrinsic capacitances, and satisfies the charge conservation condition. The fitting parameters in these equations are easily determined by the measured results with subsequent small clarifications under the optimization procedure. To predict the variations of the current–voltage characteristic and equivalent-circuit elements with temperature and self-heating, simple equations have been proposed. The presented model is a good compromise between the simplicity of the numerical calculations and the accuracy of the final results, and can be easily inserted in any circuit simulators. By analytically combining the described linear external and nonlinear intrinsic elements, high-power and low-voltage silicon MOSFETs can be completely characterized and implemented in RF circuit design.

## ACKNOWLEDGMENT

The authors would like to thank Dr. V. V. Nikiforov, Moscow Technical University of Communications and Informatics, Moscow, Russia, and Dr. E. P. Stroganova, Moscow Technical University of Communications and Informatics, Moscow, Russia, for their invaluable assistance and useful consultations during long-term joint scientific research with A. V. Grebenikov at Moscow Technical University of Communications and Informatics. The authors also acknowledge sincere appreciation to Dr. S. Xu, Institute of Microelectronics, Singapore, for presenting wafers for *S*-parameter measurements. The

authors especially wish to thank G. V. Grebennikova, Institute of Applied Physics, Moscow, Russia, for providing numerical calculations as well as her continuous encouragement and support.

## REFERENCES

- [1] N. Camilleri, J. Costa, D. Lovelace, and D. Ngo, "Silicon MOSFET's, the microwave technology for the '90s," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1993, pp. 545–548.

- [2] A. Wood, C. Dragon, and W. Burger, "A silicon MOS process for integrated power amplifiers," in *Proc. IEEE Microwave Millimeter Wave Monolithic Circuits Symp. Dig.*, 1996, pp. 189–192.

- [3] G. Ma, W. Burger, C. Dragon, and T. Gillenwater, "High efficiency LDMOS power FET for low voltage wireless communications," in *IEDM Tech. Dig.*, 1996, pp. 91–94.

- [4] A. Wood, W. Brakensiek, C. Dragon, and W. Burger, "120 Watt, 2 GHz, Si LDMOS RF power transistor for PCS base station applications," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1998, pp. 707–710.

- [5] I. Yoshida, M. Katsueda, Y. Maruyama, and I. Kohjiro, "A highly efficient 1.9 GHz Si high-power MOS amplifier," *IEEE Trans. Electron Devices*, vol. 45, pp. 953–956, Apr. 1998.

- [6] Y. P. Tsividis and K. Suyama, "MOSFET modeling for analog circuit CAD: Problems and prospects," *IEEE J. Solid-State Circuits*, vol. 29, pp. 210–216, Mar. 1994.

- [7] Y. C. Chen, D. L. Ingram, H. C. Yen, R. Lai, and D. C. Streit, "A new empirical *I*–*V* model for HEMT devices," *IEEE Microwave Guided Wave Lett.*, vol. 8, pp. 342–344, Oct. 1998.

- [8] Y. P. Tsividis, *Operation and Modeling of the MOS Transistor*. New York: McGraw-Hill, 1987.

- [9] E. Abou-Allam and T. Manku, "A small-signal MOSFET model for radio frequency IC applications," *IEEE Trans. Computer-Aided Design*, vol. 16, pp. 437–447, May 1997.

- [10] J. A. Garcia, A. Mediavilla, J. C. Pedro, N. B. Carvalho, A. Tazon, and J. L. Garcia, "Characterizing the gate to source nonlinear capacitor role on FET IMD performance," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1998, pp. 1635–1637.

- [11] J. M. Collantes, J. J. Raoux, J. P. Villote, R. Quere, G. Montoriol, and F. Dupis, "A new large-signal model based on pulse measurement technique for RF power MOSFET," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1995, pp. 1553–1556.

- [12] G. Massobrio and P. Antognetti, *Semiconductor Device Modeling with SPICE*. New York: McGraw-Hill, 1993.

- [13] P. Perugupalli, M. Trivedi, K. Shenai, and S. K. Leong, "Modeling and characterization of an 80 V silicon LDMOSFET for emerging RFIC applications," *IEEE Trans. Electron Devices*, vol. 45, pp. 1468–1478, July 1998.

- [14] D. Moncoqut, D. France, P. Rossel, G. Charitat, H. Tranduc, J. Victory, and I. Pages, "LDMOS transistor for smart power circuits: Modeling and design," in *Proc. IEEE Bipolar/BiCMOS Circuits Technol. Meeting*, 1996, pp. 216–219.

- [15] M. Bucher, C. Lallement, and C. C. Enz, "An efficient parameter extraction methodology for the EKV MOST model," in *Proc. IEEE Int. Microelectron. Test Structures Conf.*, 1996, pp. 145–150.

- [16] I. Angelov, H. Zirath, and N. Rorsman, "A new empirical nonlinear model for HEMT and MESFET devices," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 2258–2266, Dec. 1992.

- [17] T. Taki, "Approximation of junction field-effect transistor characteristics by a hyperbolic function," *IEEE J. Solid-State Circuits*, vol. SSC-13, pp. 724–726, Oct. 1978.

- [18] T. Kacprzak and A. Materka, "Compact dc model of GaAs FET's for large-signal computer calculation," *IEEE J. Solid-State Circuits*, vol. SSC-18, pp. 211–213, Apr. 1983.

- [19] Y. Chan, C. Huang, C. Weng, and B. Liew, "Characteristics of deep-submicrometer MOSFET and its empirical nonlinear RF model," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 611–615, May 1998.

- [20] C. E. Biber, M. L. Schmatz, T. Morf, U. Lott, and W. Bachtold, "A nonlinear microwave MOSFET model for SPICE simulators," *IEEE Trans. Microwave Theory Tech.*, vol. 46, pp. 604–610, May 1998.

- [21] R. Sung, P. Bendix, and M. B. Das, "Extraction of high-frequency equivalent circuit parameters of submicron gate-length MOSFET's," *IEEE Trans. Electron Devices*, vol. 45, pp. 1769–1775, Aug. 1998.

- [22] B. J. Cheu and P. K. Ko, "Measurement and modeling of short-channel MOS transistor gate capacitances," *IEEE J. Solid-State Circuits*, vol. SC-22, pp. 464–472, June 1987.

- [23] M. C. Ho, K. Green, R. Culbertson, J. Y. Yang, D. Ladwig, and P. Ehnis, "A physical large signal Si MOSFET model for RF circuit design," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1997, pp. 391-394.

- [24] R. E. Anholt and S. E. Swirhun, "Experimental investigations of the temperature dependence of GaAs FET equivalent circuits," *IEEE Trans. Electron Devices*, vol. 39, pp. 2029-2036, Sept. 1992.

- [25] W. R. Curtice, J. A. Pla, D. Bridges, T. Liang, and E. E. Shumate, "A new dynamic electro-thermal nonlinear model for silicon RF LDMOS FETs," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1999, pp. 419-422.

**Andrey V. Grebennikov** (M'99) was born in Uzhgorod, Russia, in 1956. He received the Dipl. Ing. degree from the Moscow Institute of Physics and Technology, Moscow, Russia, in 1980, and the Ph.D. degree from the Moscow Technical University of Communication and Informatics, Moscow, Russia, in 1991, respectively.

From 1983 to 1998, he was a Senior Scientist in the Scientific Research Department and as an Associate Professor in the Telecommunication Management Department, Moscow Technical University of Communications and Informatics. His research interests included the design and development of power FM broadcasting and very high frequency (VHF)-UHF TV transmitters, hybrid RF and microwave high efficiency and broad-band linear high-power amplifiers, and single-frequency and voltage-controlled oscillators using bipolar and FET devices. Since October 1998, he has been a Member of Technical Staff at the Institute of Microelectronics, Singapore. His current research interests include the design and development of hybrid and monolithic ICs of RF and microwave LDMOSFET power amplifiers, RF MOSFET modeling, and microwave oscillator CAD design.

**Fujiang Lin** (M'93-SM'99) received the B.S.E.E. and M.S.E.E. degrees from the University of Science and Technology of China (USTC), Hefei, China, in 1982 and 1984, respectively, and the Dr.-Ing. degree from the Universität Kassel, Kassel, Germany, in 1993, all in microwave and RF engineering.

From 1984 to 1986, he was a Teaching and Research Assistant at the USTC, where he was involved in the areas of electromagnetic-field theory and microwave antennas. From 1987 to 1989, he was a Research Engineer at the Technische Universität Hamburg-Harburg, Hamburg-Harburg, Germany, where he was involved with the theoretical investigation of microwave oven optimization and CAD for millimeter-wave coupled-cavity traveling-wave tubes. From 1989 to 1993, he was a Research Engineer at the Universität Kassel, where he focused on experimental modeling of high-performance microwave GaAs FETs. From 1993 to 1995, he was a Research Scientist at the National University of Singapore (NUS), Singapore, where his research activities include microwave measurement techniques, large-signal FET modeling and hybrid microwave integrated circuits (MICs). In 1995, he joined the Institute of Microelectronics (IME), Singapore, as a Member of Technical Staff, where he began to set up an RF modeling laboratory in supporting MMIC/RF IC new development. He later became a Project Manager of multiple chip module (MCM) design for microwave applications. Since August 1999, he has been with Agilent Technologies (previously HP EEsos), Singapore, as the Technical Director to lead a newly set up Singapore Microelectronics Modeling Center in providing accurate state-of-the-art device and package characterization and modeling solution service worldwide. As an Adjunct Associate Professor at NUS, he is actively involved in educating and training post-graduate students. He has authored or co-authored over 40 scientific papers. He is listed in the 1997 *International Who's Who of Professionals, Who's Who of the Asian Pacific Rim, and Who's Who of the World*. He organized a GaAs modeling workshop at the 1999 Asia-Pacific Microwave Conference (APMC'99).

Dr. Lin has served on the chapter committees of the Singapore sections for the IEEE Microwave Theory and Techniques Society (IEEE MTT-S), the IEEE Antennas and Propagation Society (IEEE AP-S), and the IEEE Electromagnetic Compatibility Society since 1996. He was the recipient of the 1998 Innovator Award presented by *EDN Asia Magazine*.