# Calibratable Adaptive Antenna Combiner at 5.2 GHz with High Yield for Laptop Interface Card

Frank Ellinger, *Student Member, IEEE*, Rolf Vogt, and Werner Bächtold, *Fellow, IEEE*

**Abstract**—This paper presents a calibratable adaptive antenna combiner with three branches for high-performance radio local area network at 5.2 GHz. The system was mounted on a reinforced duroid substrate and enables the integration in a laptop interface card. Each branch consists of a bent stacked slot antenna, a low-noise-amplifier monolithic microwave integrated circuit (MMIC) with antenna/calibration switching and a vector modulator MMIC with an amplitude control range of 15 dB and 360° phase control range. The signals of the three branches are combined by an active adder MMIC. A calibration is proposed to significantly improve the phase and amplitude control resolution and the yield of the designed MMIC circuits, which were fabricated using a commercial GaAs process. Each branch has a maximum power gain of 16 dB, a noise figure of 3.3 dB, and a 1-dB output compression point of  $-4$  dBm. The whole system draws less than 28 mA from a 2.7-V voltage supply. The total required MMIC chip size is 10.8 mm<sup>2</sup>.

**Index Terms**—Amplitude control, GaAs MESFET, HIPERLAN, MMIC, phase control, smart antennas, vector modulator.

## I. INTRODUCTION

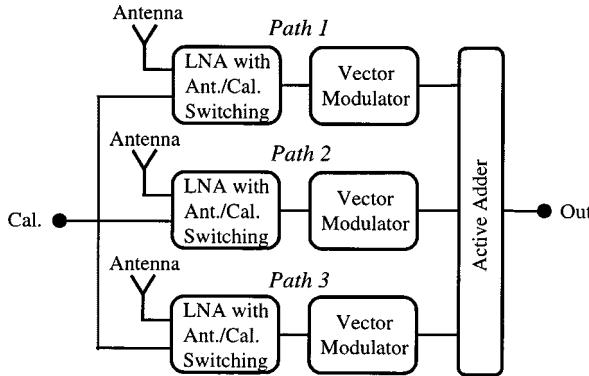

THE high-performance radio local area network (HIPERLAN) standard at 5.2 GHz plays a growing role in the area of wireless LAN systems. Serious challenges are its high bit rate of 23.5 Mbit/s and its peer-to-peer approach, which allows direct communication between terminals without requiring a central base station. To counteract the time dispersive nature of the indoor radio channel, the use of adaptive antenna combining has been proposed [1]. It has been successfully shown in [2] that even arrays with only three or four active antennas can strongly reduce intersymbol interferences, resulting in a significant improvement of the bit error rate (BER). However, precise amplitude control elements and phase shifters with phase control ranges of 360° are required for this purpose to successfully compete with the performance of approaches using costly baseband equalizer techniques. This paper presents an adaptive antenna combiner with three branches, which has been mounted on a 2 in  $\times$  2 in  $\times$  0.1 in duroid substrate with reinforced backplane. Its size allows the integration in a laptop interface card, protruding out of a terminal (e.g., a laptop), as illustrated in Fig. 1. The Personal Computer Memory Card International Association (PCMCIA) standard is applied for this interface card. Each branch of the combiner consists of a bent stacked slot antenna (BSSA) [3], an

Fig. 1. Example of a PCMCIA card used for laptops.

LNA monolithic microwave integrated circuit (MMIC), and a vector-modulator MMIC for amplitude and phase control. The signals of the three branches are combined by an active signal adder MMIC.

Passive attenuators [4] and variable gain amplifiers (VGAs) [5] are frequently used to control the amplitude in adaptive antenna receivers. Reflective-type phase shifters [6] and switched high-pass/low-pass phase shifters [7] are among the most important techniques for phase shifting. In comparison to these components, vector modulators [8] are excellent alternatives and have been chosen for this system, because they are able to adjust both amplitude and phase in the same circuit, are well suited for monolithic integration, require only a relatively small chip area, and have the ability to provide gain. Our vector modulator uses VGAs, which provide large amplitude control ranges to enable continuous amplitude and phase control ranges of 15 dB and 360° by weighting and combining three vectors with phase offsets of 120°.

However, process tolerances, ambient temperature variations, and frequency dependences limit the precision of the required vectors, which are calculated in the baseband algorithm [9]. This algorithm uses the measured data of the received signal vectors of each branch and calculates the optimum vector coefficients of the branches for minimum BER of the system. Constant phase and amplitude errors, which are, for example, caused by the antenna, LNA, adder, and their interconnects have already been considered in these calculations and do not effect the BER. Relative errors, which are caused by the amplitude and phase control elements—in our case, the vector modulators, significantly degrade the BER. A calibration is proposed to circumvent these errors by feeding a switchable calibration signal into the LNA, which is located in front of the vector modulator, as illustrated in Fig. 2.

The Triquint TQTRx GaAs process, which provides MESFETs with gate lengths of 0.6  $\mu$ m and inductors with a quality factor of approximately 20, is used for the monolithic-microwave integrated-circuit (MMIC) designs. Large- and

Manuscript received February 29, 2000; revised August 25, 2000.

The authors are with the Laboratory for Electromagnetic Fields and Microwave Electronics, Swiss Federal Institute of Technology Zürich, CH-8092 Zürich, Switzerland (e-mail: ellinger@ifh.ee.ethz.ch).

Publisher Item Identifier S 0018-9480(00)10751-3.

Fig. 2. Architecture of the adaptive antenna combiner with three branches. Cal.: calibration input.

small-signal simulations were performed with HP Libra using a modified TOM II MESFET model [10]. Noise behavior was simulated using measured noise figure data of the FETs.

## II. LNA WITH ANTENNA/CALIBRATION SWITCHING

Single-pole double-throw (SPDT) switches, which require two control voltages, are frequently used to enable switching between two different signal channels. Two placements for such an SPDT switch are imaginable to enable the feed of a calibration signal for the vector modulator calibration: the SPDT switch could be placed in front of the LNA or between the LNA and the vector modulator. However, the resistive parasitics of the series FETs of an SPDT switch would especially degrade the noise performance of the system when located in front of the LNA, whereas the placement of an SPDT switch between the LNA and vector modulator would degrade the calibration precision. This is caused by the impedance change in front of the vector modulator from the LNA output impedance to the calibration input impedance, which effects the VGA characteristics of the vector modulator.

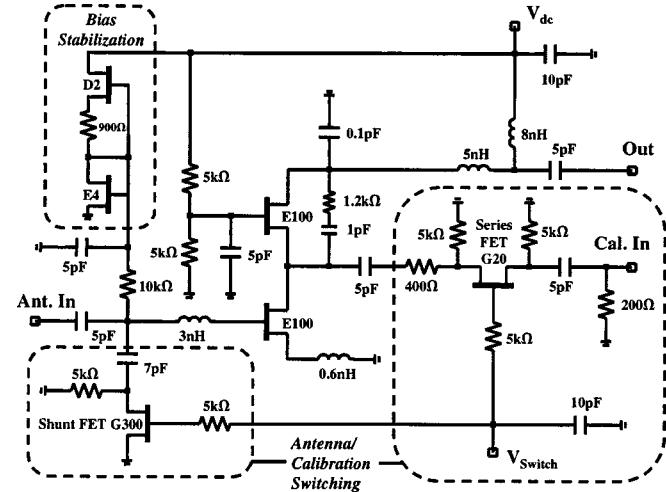

To circumvent these problems, we propose a cascode LNA with integrated antenna/calibration switching, as shown in Fig. 3. Cold deep-depletion FETs (G-FETs) are used to enable switching between the antenna and calibration signals with only one control voltage ( $V_{\text{Switch}}$ ). A shunt FET with a gatewidth of  $300 \mu\text{m}$  is located at the antenna input of the LNA to enable antenna to calibration isolation, whereas a series FET with a gatewidth of  $20 \mu\text{m}$  enables calibration to antenna isolation. The common source circuit isolates the shunt FET from the calibration input, while the common gate circuit isolates impedance changes of the switching modes to ensure a constant LNA output impedance. The LNA calibration input is matched to  $150 \Omega$  to enable  $50\text{-}\Omega$  match of the overall calibration input of the system, which connects the three LNA calibration inputs together. The antenna input and output are reactively matched to  $50 \Omega$ . Enhancement FETs (E-FETs) with gatewidths of  $100 \mu\text{m}$  are used to reach high gain, while consuming minimum dc current.  $RC$  feedback is applied to the common gate FET to improve RF stability and to make the circuit more broad band. The source of the common source FET is inductively degenerated to improve noise performance,

Fig. 3. Circuit schematic of the LNA with calibration/antenna switching, antenna mode ( $V_{\text{Switch}} = -3 \text{ V}$ , antenna: on, calibration: off). Calibration mode ( $V_{\text{Switch}} = 0 \text{ V}$ , antenna: off, calibration: on).

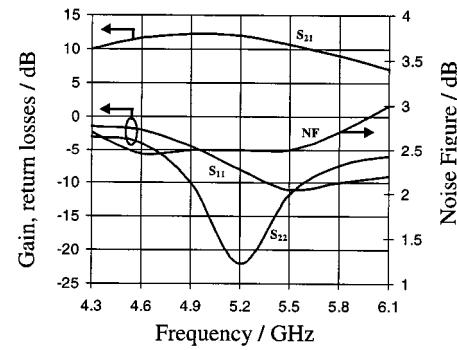

Fig. 4. Measured gain, noise figure, and input and output return loss of the LNA with antenna/calibration switching, switching mode: antenna on, calibration off ( $V_{\text{dc}} = 2.7 \text{ V}$ ,  $I_{\text{dc}} = 2.6 \text{ mA}$ ).

input matching, and intermodulation performance. The gates are biased by high-value resistors. The drain of the common gate FET is biased with an inductance and its gate is terminated with a large capacitor. A bias stabilization circuit is applied to the gate of the common source FET to decrease effects of threshold voltage variations and to ensure a nominal dc current of  $2.6 \text{ mA}$ . The bias stabilization circuit consists of an E-FET and a depletion FET (D-FET) with strong resistive feedback and consumes a dc current of  $60 \mu\text{A}$ .

Fig. 4 shows the measured gain, noise figure, and return losses of the LNA in the antenna mode ( $V_{\text{Switch}} = -3 \text{ V}$ , antenna: on, calibration: off). At a supply voltage of  $2.7 \text{ V}$ , the gain is  $12 \text{ dB}$  and the noise figure is  $2.5 \text{ dB}$ . The 1-dB output compression point is  $-2 \text{ dBm}$  and the input and output return losses are  $7 \text{ dB}$  (noise match) and  $22 \text{ dB}$ , respectively. The calibration to output isolation is  $33 \text{ dB}$ . In the calibration mode ( $V_{\text{Switch}} = 0 \text{ V}$ , antenna: off, calibration: on) the loss is  $12 \text{ dB}$ . The requirements for the noise performance in this mode are not demanding because a strong local calibration signal is used, providing a sufficient signal-to-noise ratio. The antenna to output isolation is  $20 \text{ dB}$ .

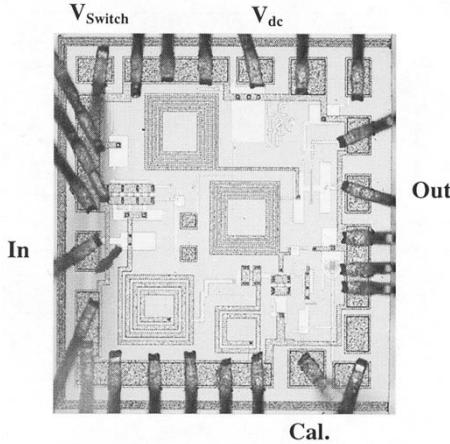

Fig. 5 shows a photograph of the bonded MMIC chip with a chip size of  $1 \text{ mm} \times 0.9 \text{ mm}$ .

Fig. 5. LNA MMIC with antenna/calibration.

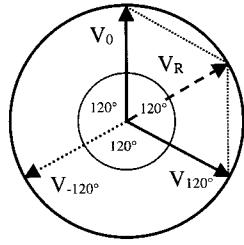

Fig. 6. Vector addition: every phase with amplitude  $V_R$  can be obtained by weighting the vectors  $V_0$ ,  $V_{120^\circ}$  and  $V_{-120^\circ}$ .

### III. CALIBRATABLE VECTOR MODULATOR

Usually four signal paths with phase offsets of  $90^\circ$  are used for vector modulators. To minimize chip size and control complexity, we use only three signal paths with phase offsets of  $120^\circ$ . Every phase between  $0^\circ$  and  $360^\circ$  with amplitude  $V_R$  can be obtained by weighting the amplitudes of the paths, as illustrated in Fig. 6.

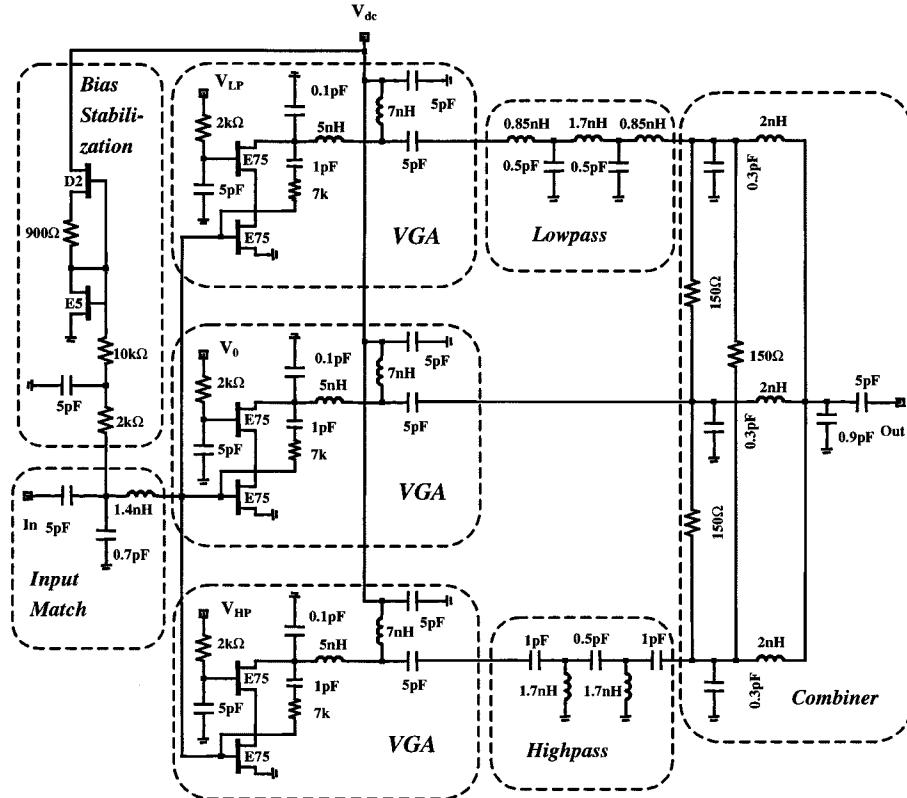

The simplified circuit schematic of the vector modulator is shown in Fig. 7. Input and output are matched to  $50 \Omega$ . Low power-consuming E-FETs with gatewidths of  $75 \mu\text{m}$  are used for the VGAs, which divide the input signal. Cascode configurations are applied because their variation of the input and output impedances versus gain is much smaller than in VGAs using single transistors [11], which is important to improve the quasi-ideal power divider/combiner function of the vector modulator over the whole amplitude range. The use of the proposed calibration (see the following section) would otherwise cause impedance variations, which would generate phase and amplitude errors. A further advantage of cascode circuits is that they provide large amplitude control ranges and high gain. The VGAs are reactively matched and the amplitude of the different phase paths can be controlled by varying the gate control voltages ( $V_{LP}$ ,  $V_0$ ,  $V_{HP}$ ) of the common gate FETs. A bias stabilization circuit similar to the one used for the LNA is applied to the gates of the common source FETs to decrease effects of threshold voltage variations and to ensure a nominal dc current of  $1.6 \text{ mA}$  per path, when the corresponding control voltage is set for maximum gain.

The phase offsets of  $\pm 120^\circ$  are generated by  $LC$  high- and low-pass structures. Simulations show insertion losses of lower than  $2 \text{ dB}$  within the frequency range between  $4.8$ – $5.8 \text{ GHz}$ . The three paths are added by a modified Wilkinson combiner using lumped elements. Simulations show that this combiner has a loss of  $6 \text{ dB}$  per path and a port-to-port isolation of over  $20 \text{ dB}$  within the frequency range between  $4.8$ – $5.8 \text{ GHz}$ .

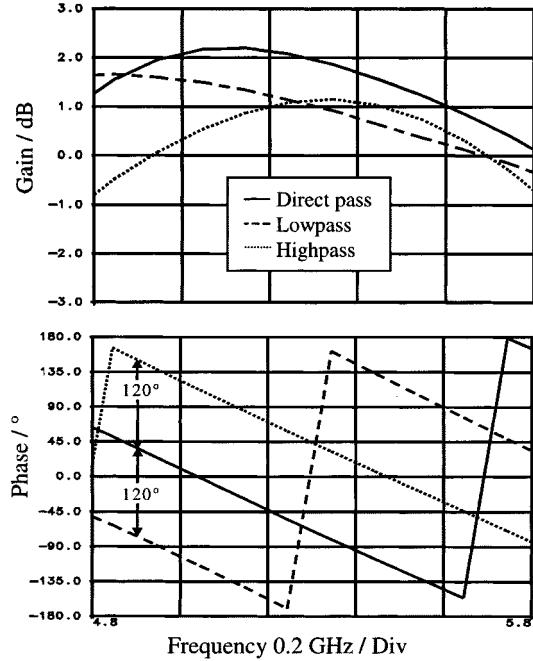

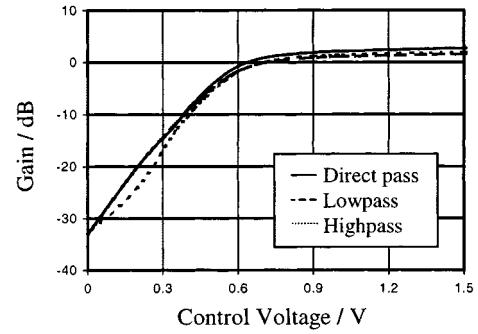

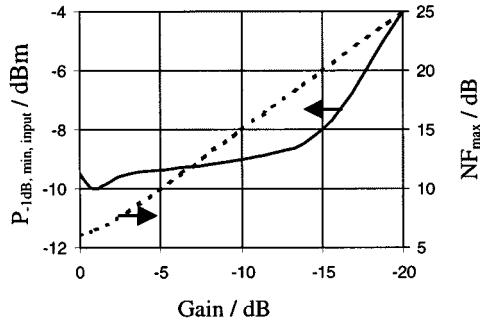

Fig. 8 shows the measured gain and phase of each of the three paths versus frequency at maximum gain (control voltage =  $1.5 \text{ V}$ ), while the other two paths are switched off. Within  $4.8$  and  $5.8 \text{ GHz}$ , the losses of the paths are less than  $0.7 \text{ dB}$  and the phase offsets between the three paths are  $120^\circ$ . Fig. 9 shows the measured gain of each of the three paths versus control voltage at a frequency of  $5.2 \text{ GHz}$ . The amplitude control range of the VGAs is  $33 \text{ dB}$ . Due to this large gain control range, phase as well as amplitude can be controlled with this vector modulator. Fig. 10 shows the noise and compression performance of the vector modulator versus gain at  $5.2 \text{ GHz}$ , when one path is active and two paths are switched off (this is the worst case). The noise figure at maximum gain is  $6 \text{ dB}$  and is increasing with decreasing gain. Within the whole gain control range, the  $1\text{-dB}$  input compression point is higher than  $-10 \text{ dBm}$ . The maximum current consumption per path is  $1.6 \text{ mA}$ ; thus, the maximum current consumption of the vector modulator is  $3.2 \text{ mA}$  from a supply voltage of  $2.7 \text{ V}$ .

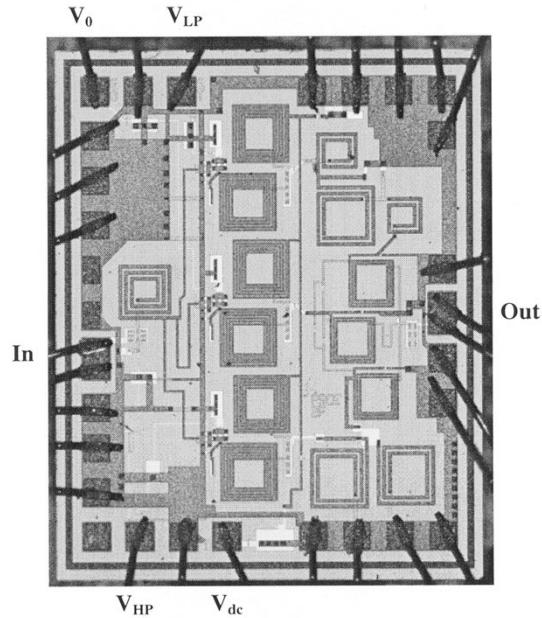

Fig. 11 shows a photograph of the vector modulator MMIC; the chip size is  $1.7 \text{ mm} \times 1.4 \text{ mm}$ .

#### A. Calibration

A calibration signal can be fed as shown in Fig. 2. With the assumption of an ideal divider/combiner, we can assume that the different paths are isolated from each other. Thus, the output vector of the vector modulator can be calculated as a function of the vectors of each single path. We propose the following two-step calibration procedure.

- Step 1) Measurement of the gain and phase versus control voltage of each of the three paths, while the other two paths are switched off.

- Step 2) Calculation of the corresponding control voltages for a desired phase and amplitude by vector addition, using the data from step 1).

The baseband signal processor can be used for this task. If the transmitting frequency is changed or if the receiver has to adapt to temperature variations, the calibration procedure can be repeated.

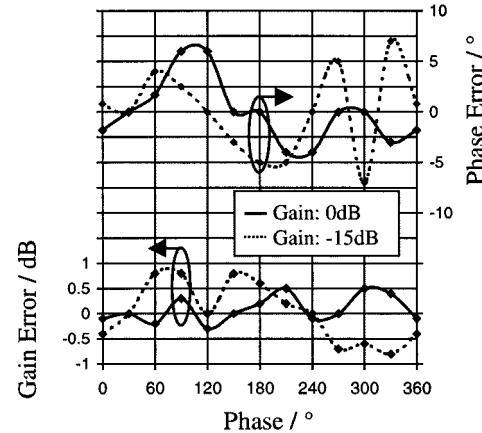

To validate the proposed calibration procedure, measurements are compared with ideal calculations given by the calibration procedure. Fig. 12 shows the resulting phase and gain errors, which are, in particular, created by the nonideal divider/combiner function of the circuit. As expected, the errors increase with decreasing gain because the performance of the quasi-ideal divider is degrading. For a gain of  $0 \text{ dB}$ , the errors are below  $\pm 0.5 \text{ dB}$  and  $\pm 6^\circ$ , for a gain of  $-15 \text{ dB}$ , the errors are below  $\pm 0.8 \text{ dB}$  and  $\pm 9^\circ$ . System simulations show that those precisions are well suited for smart antenna receivers [9]. Note that the requirements for the precision and for the

Fig. 7. Circuit schematic of the vector modulator.

Fig. 8. Measured phase and gain of the individual paths of the vector modulator versus frequency at a control voltage of 1.5 V ( $V_{dc} = 2.7$  V,  $I_{dc} = 2$  mA).

noise fall with decreasing gain. If all paths are switched off, the attenuation is 33 dB. This mode is used to select the different branches of the system for calibration.

Fig. 9. Measured gain of each of the three paths of the vector modulator versus control voltage, while the other paths are switched off ( $V_{dc} = 2.7$  V,  $f = 5.2$  GHz).

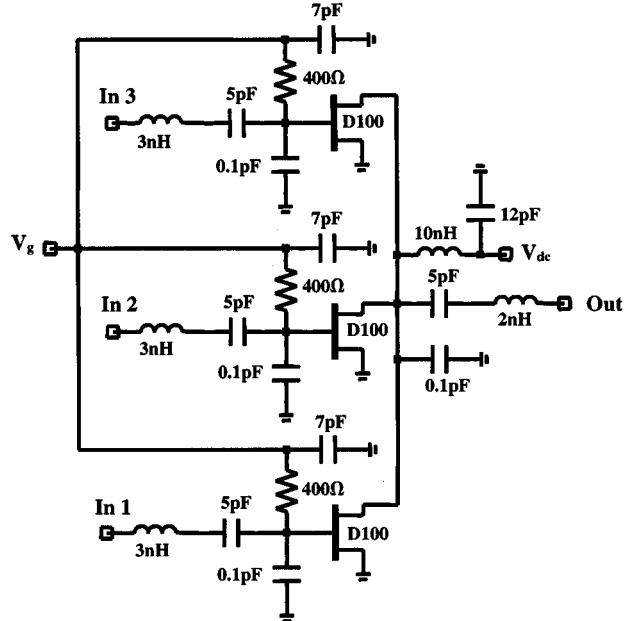

#### IV. ACTIVE ADDER

Fig. 13 shows the simplified circuit schematic of the active adder, which combines the signals of the three branches of the system. The input signals ( $I_1$ ,  $I_2$ ,  $I_3$ ) are fed through the gates of the FETs, the signals are added by connecting the drains together. D-FETs with gatewidths of 100  $\mu$ m are used, showing excellent large-signal performance, while consuming minimum dc current. The inputs and the output are reactively matched to 50  $\Omega$ . The gates are biased by resistors, which improve stability and make the circuit more broad band. The drains are biased by an inductor.

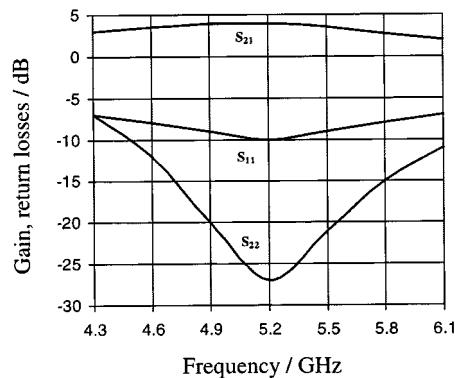

Fig. 14 shows the measured gain and the input and output return loss at a supply voltage of 2.7 V and a total current consumption of 10.8 mA. At 5.2 GHz, the gain is 4 dB, the 1-dB

Fig. 10. Measured maximum noise figure ( $NF_{\max}$ ) and minimum 1-dB compression point at the input ( $P_{-1 \text{ dB}, \min, \text{input}}$ ) versus gain of the vector modulator  $V_{dc} = 2.7 \text{ V}$ ,  $f = 5.2 \text{ GHz}$ .

Fig. 11. Vector modulator MMIC (chip size is  $1.7 \text{ mm} \times 1.4 \text{ mm}$ ).

output compression point per branch is 7 dBm and the input and output return losses are 10 and 27 dB, respectively.

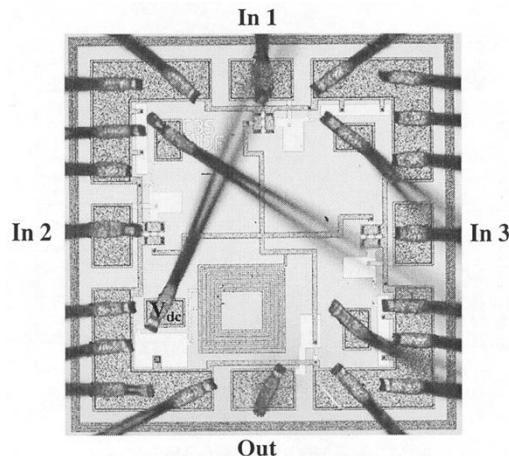

Fig. 15 shows a photograph of the bonded adder MMIC chip, which has a size of  $1 \text{ mm} \times 1 \text{ mm}$ .

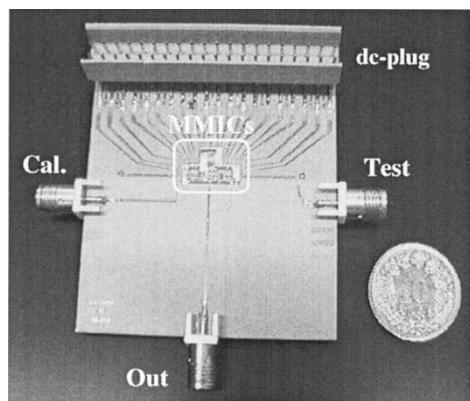

## V. ADAPTIVE COMBINER

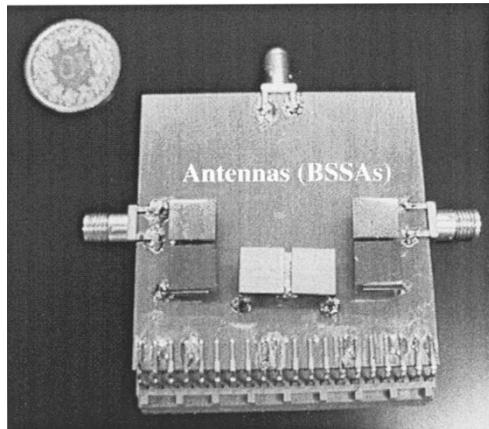

The MMIC chips were mounted on a duroid substrate with a dielectric constant of  $\epsilon_r = 10.2$  and a size of  $2 \text{ in} \times 2 \text{ in} \times 0.1 \text{ in}$ , as shown in Fig. 16. SMA connectors are mounted to enable RF measurements. A plug with several pins is mounted to feed the circuits with the ten required dc control voltages (nine for the vector modulators and one for antenna/calibration switching) and the supply voltage. The BSSAs [3] are mounted on the reinforced back metal of the substrate. The back metal is used as the common ground plane of the antennas, as shown in Fig. 17. Due to their compact size ( $16 \times 8 \times 5.2 \text{ mm}^3$ ), low costs (easily manufactured from one thin sheet of metal and tolerant to manufacturing inaccuracies), large bandwidth of 30%, high efficiency

Fig. 12. Measured phase and gain error of the vector modulator at a gain of 0 dB (maximum gain) and  $-15 \text{ dB}$ , respectively, versus expected phase, obtained using the calibration ( $V_{dc} = 2.7 \text{ V}$ ,  $f = 5.2 \text{ GHz}$ ).

Fig. 13. Circuit schematic of the active adder, which combines the signals of the three branches.

Fig. 14. Measured gain and input and output return loss of the active adder ( $V_{dc} = 2.7 \text{ V}$ ,  $V_G = -0.3 \text{ V}$ ,  $I_{dc} = 10.8 \text{ mA}$ ).

Fig. 15. Active adder MMIC (chip size is 1 mm  $\times$  1 mm).

Fig. 16. Front of the adaptive combiner with three branches (size of the duroid substrate: 2  $\times$  2 in).

Fig. 17. Backside of the adaptive combiner with three branches.

of 90%, and an antenna gain of 4 dBi, these antennas excellently fulfill the requirements for wireless LAN applications.

Table I summarizes the performances of the system. Each branch has a maximum power gain of 16 dB, a noise figure of 3.3 dB, and an 1-dB output compression point of  $-5$  dBm. Depending on the number of activated paths in the vector modulators, the minimum and maximum current consumption of the whole system using a 2.7-V supply is only 20.2 and 28.2 mA, respectively. Phase and gain control performances are reached,

TABLE I

SUMMARIZED PERFORMANCES OF THE ADAPTIVE COMBINER AT 5.2 GHz

|                                                       |                                 |

|-------------------------------------------------------|---------------------------------|

| Maximum power gain per branch                         | 16dB                            |

| Antenna gain per branch                               | 4dBi                            |

| Noise figure per branch                               | 3.3dB                           |

| 1dB output compression point per branch               | $-5$ dBm                        |

| Amplitude control range / max. attenuation per branch | 15dB / 33dB                     |

| Phase control range per branch                        | 360°                            |

| Max. amplitude errors per branch                      | $\pm 0.8$ dB                    |

| Max. phase errors per branch                          | $\pm 9$ °                       |

| Output return loss                                    | 25dB                            |

| Loss of the calibration signal                        | 12dB                            |

| 1dB calibration input compression point per branch    | $-5$ dBm                        |

| Supply voltage                                        | 2.7V                            |

| Min. / max. current consumption                       | 20.2mA / 28.2mA                 |

| Size of the substrate                                 | 2in $\times$ 2in $\times$ 0.1in |

| Required GaAs MMIC chip size                          | $\sim 11$ mm $^2$               |

| Total number of control voltages                      | 10                              |

as described in Section III. The required GaAs chip size for the whole system is 11 mm $^2$ .

## VI. CONCLUSION

A calibratable adaptive antenna combiner with three branches for HIPERLAN at 5.2 GHz has been presented in this paper. The system was mounted on a reinforced duroid substrate and is well suited for PCMCIA card integration. It consists of three BSSAs and highly integrated MMIC circuits (three LNAs with calibration switching, three vector modulators for amplitude and phase control, and an active signal adder). A calibration is proposed to significantly improve the production yield, the operation bandwidth, and to compensate the effects of temperature variations. Due to its low power consumption and its low-cost design, the system is a potential alternative to approaches using costly baseband equalizer techniques.

## ACKNOWLEDGMENT

The authors would like to thank U. Fritsch, Ascom, Mägenwil, Switzerland, F. Wandler, Ascom, Mägenwil, Switzerland, and M. Kuhn, University of Saarbrücken, Saarbrücken, Germany, for their constructive discussions, M. Lanz, Swiss Federal Institute of Technology, Zürich, Zürich, Switzerland, for laboratory works and T. Brauner, Swiss Federal Institute of Technology, Zürich, Zürich, Switzerland, F. Robin, Swiss Federal Institute of Technology, Zürich, Zürich, Switzerland, and D. Treyer, Swiss Federal Institute of Technology, Zürich, Zürich, Switzerland, for reviewing this paper's manuscript.

## REFERENCES

- [1] A. Wittneben and U. Dettmar, "A low cost noncoherent receiver with adaptive antenna combining for high speed wireless LANs," in *IEEE 47th Veh. Technol. Conf.*, vol. 1, May 1997, pp. 173–177.

- [2] A. Wittneben and U. Dersch, "On the potential of adaptive antenna combining for intersymbol interference reduction in high speed wireless LANs," in *IEEE 47th Veh. Technol. Conf.*, vol. 2, May 1997, pp. 627–631.

- [3] M. Liebendorfer and U. Dersch, "Wireless LAN diversity antenna system for PCMCIA card integration," in *IEEE 47th Veh. Technol. Conf.*, vol. 3, May 1997, pp. 2022–2026.

- [4] S. Dingo, R. Meierer, and R. North, "Computer-aided design of MMIC variable attenuators," *Microwave J.*, pp. 134–140, Nov. 1997.

- [5] F. Ellinger, U. Lott, and W. Bächtold, "A 5.2 GHz variable gain LNA MMIC for adaptive antenna combining," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, Anaheim, CA, June 1999, pp. 87-89.

- [6] F. Di Paolo, "A simple, high yield 6 to 18 GHz GaAs monolithic phase shifter," *Microwave J.*, pp. 92-104, Apr. 1997.

- [7] J. Wallace, H. Redd, and R. Furlow, "Low cost MMIC DBS chip sets for phased array applications," in *IEEE MTT-S Int. Microwave Symp. Dig.*, vol. 2, Anaheim, CA, June 1999, pp. 677-680.

- [8] J. Grajal, J. Gismero, M. Mahfoudi, and F. A. Petz, "A 1.4-2.7 GHz analog MMIC vector modulator for a crossbar beamforming network," *IEEE Trans. Microwave Theory Tech.*, vol. 45, pp. 1705-1714, Oct. 1997.

- [9] F. Königsstein, "Development and assessment of algorithms for the adaption and calibration of an antenna array," Diploma thesis, Dept. Telecommun., Univ. Saarbrücken, Saarbrücken, Germany, 1999.

- [10] F. Ellinger, J. Kucera, and W. Bächtold, "Improvements on a nonlinear GaAs MESFET model," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Baltimore, MD, June 1998, pp. 1623-1626.

- [11] J. P. Mondal, A. G. Milnes, G. Oakes, and S. K. Wang, "Phase shifts in single- and dual-gate GaAs MESFET's for 2-4 GHz quadrature phase shifters," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 1280-1287, Oct. 1984.

**Frank Ellinger** (S'97) was born in Friedrichshafen, Germany, in 1972. He received the Masters degree in electrical engineering from the University of Ulm, Ulm, Germany, in 1996, and is currently working toward the Masters in managerial economics and the Ph.D. degree in electrical engineering from the Swiss Federal Institute of Technology (ETH), Zürich, Switzerland.

Since 1997, he has been a Teaching Assistant with the ETH. His research work is mainly concerned with the design of low-power-consuming MMIC components for smart antenna receivers.

**Rolf Vogt** received the Masters degree in electrical engineering and Ph.D. degree from the Swiss Federal Institute of Technology (ETH), Zürich, Switzerland, in 1988 and 1996, respectively.

From 1988 to 1990, he was a Development Engineer for ALCATEL Switzerland, where he was involved in the area of microwave electronics. From 1990 to 1996, he was with the Laboratory for Electromagnetic Fields and Microwave Electronics, ETH, where his main research interest were the design of mixed-signal gallium-arsenide integrated circuits. From 1997 to 1999 he was a Project Manager in the Physical Electronics Laboratory, ETH, where he was responsible for the Circuit Design Group, as well as for the Magnetic Sensor Group. He was also a Technical Coordinator of a European ESPRIT Project, in which integrated circuits for industrial switch and sensor applications have been developed. Since 2000, he has been the Head of the RF Integrated Circuit (RF IC) Design Group, Laboratory for Electromagnetic Fields and Microwave Electronics, ETH.

**Werner Bächtold** (M'71-SM'99-F'00) received the Diploma degree and Ph.D. degree in electrical engineering from the Swiss Federal Institute of Technology (ETH) Zürich, Zürich, Switzerland, in 1964 and 1968, respectively.

From 1969 to 1987, he was with the IBM Zürich Research Laboratory. Since December 1987, he has been a Professor of electrical engineering at the ETH, where he is also heading the Microwave Electronics Group, Laboratory for Electromagnetic Fields and Microwave Electronics. He has made professional contributions to the fields of small-signal and noise behavior of bipolar transistors and GaAs MESFETs, microwave amplifier design, design of Josephson devices and circuits, and design of semiconductor lasers. In his current activity, his group is involved in the design and characterization of GaAs MESFET and high electron-mobility transistor (HEMT) MMICs, InP-HEMT device and circuit technology, and modeling, characterization, and applications of semiconductor lasers and integrated optics.